# Modeling of Switching Power Losses in Cascaded H-Bridges with Unipolar PWM

Sobhan Mohamadian\*, *Member, IEEE*, Mohammad Modarres<sup>†</sup>, Francesco Simonetti<sup>‡</sup>, *Student Member, IEEE*, and Carlo Cecati<sup>§</sup>, *Fellow, IEEE*

Abstract—This paper studies the extraction of an equivalent resistance for calculation of the switching power losses in cascaded H-bridge multilevel inverters with unipolar pulse width modulation. The concept of local and global rms currents and switching power losses are introduced in each H-bridge considering different frequencies of the inverter output and the switching network, i.e., transistor and diode. Energy conservation law has been utilized to show that the equivalent averaged local and global resistances for switching power losses are functions of load power factor angle, load rms current, and modulation index. This dependency is then reduced to only load rms current when the equivalent resistances are transformed to the inverter output branch based on the reflection rule. Consequently, a resistive model of switching power losses of the inverter is deduced, which depends neither on the knowledge of the physics of the switch, nor on complicated nonlinear equations of the semiconductor devices, and loop inductances. Double-pulse tests are conducted to acquire reliable data on the switching characteristics of the devices for different operating points.

*Index Terms*—Energy efficiency, IGBT, inverters, MOSFET, pulse width modulation, switching loss.

### I. INTRODUCTION

WITCHING and conduction losses of semiconductor devices account for a significant amount of losses in power electronics converters. Based on the converter topology, e.g., in voltage-source inverters (VSI), dead-time voltage drop adds to the above-mentioned losses. The conduction voltage drop of each semiconductor device arises from its on state resistance and threshold voltage. On the other hand, switching and dead-time voltage drops are due to the devices' turn on and turn off delay times. These losses form a significant portion of the converter nonlinear effects, specifically at low voltages and, if not properly compensated, may deteriorate the converter performance [1], [2]. In many applications, the inverter voltage drops are modeled as an equivalent resistance and the difference between the real output voltage and the reference waveform is compensated by adding a relevant value to the reference in phase with the output current [1]-[3]. Furthermore, this equivalent resistance can be included in

\* Sobhan Mohamadian is with the Department of Information Engineering, Computer Science and Mathematics, University of L'Aquila, 67100 L'Aquila, Italy, e-mail: sobhan.mohamadian@univaq.it.

† Mohammad Modarres is with the Istituto Nazionale di Ricerca Metrologica, Turin, Italy, e-mail: m.modarres@inrim.com.

<sup>‡</sup>Francesco Simonetti is with the Department of Information Engineering, Computer Science and Mathematics, University of L'Aquila, 67100 L'Aquila, Italy, e-mail: francesco.simonetti1@graduate.univaq.it.

§ Carlo Cecati is with the Department of Information Engineering, Computer Science and Mathematics, University of L'Aquila, and DigiPower srl, 67100 L'Aquila, Italy, e-mail: carlo.cecati@univaq.it.

the averaged small-signal model of the converter for a more accurate understanding of the converter dynamics [4].

Thus, modeling of these losses is necessary for the purpose of optimum operation and control, thermal management, and efficiency estimation of converters. So far, various approaches were presented in the literature for the sake of estimation and compensation of semiconductor losses in power electronics converters, for example [3], [5]–[9] to name a few. In some of these references, the integrated effect of conduction, switching, and dead-time are estimated in the form of converter (mostly inverters) nonlinear characteristics through different tests such as the dc current test [1]–[3], [5], [6]. In other publications, for instance in [8]–[10], the individual effect of dead-time, parasitic capacitances, and conduction losses are estimated, respectively. The above-mentioned losses are functions of modulation and switching scheme [10]–[12].

In [13]- [16], theoretical approaches were presented for the estimation of the switching power losses in conventional twolevel inverters. In [17], numerous measurements were carried out in order to find the effective parameters in the switching loss model of two-level inverters and, then, the mathematical model of switching losses was extracted via curve fitting. In multilevel converters, the individual model of each device of a neutral point clamped (NPC) multilevel inverter was obtained according to its datasheet [18], then, the analysis of switching losses was performed based on the extracted model and extensive simulations under various modulation indices and power factor angles. However, the switching characteristics of the device from its datasheet are for specific working points and it cannot be applied "as is" to various permutations of contributing factors. A similar procedure was followed in [12], where massive calculations were conducted to compute the switching losses in an NPC multilevel inverter under different working conditions. In [19], conduction and switching losses of series or parallel-connected H-bridges (HBs) were compared for the purpose of selecting appropriate multilevel cascaded H-bridge (CHB) configuration. These losses were estimated under the condition of constant load voltage and varying current. However, the measurement or calculation procedure for losses was not addressed explicitly.

In this paper, the equivalent resistance for switching losses of a generic multilevel CHB inverter is estimated, when a phase-shifted unipolar pulse width modulation (PS-UPWM) is utilized. According to the above explanations, in addition to the switching characteristics such as switching delay times, the switching losses of each individual device in inverters depend upon the instantaneous current to be commutated, hence, modulation algorithm, load power factor angle, and

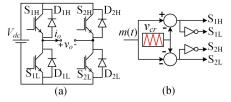

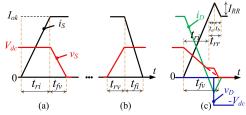

Fig. 1. Generic HB and its switching, (a) circuit and (b) Unipolar PWM.

modulation index are the contributing factors to the switching losses of the power

In this regard, in Section II, the linearized equations for the voltage and current waveforms of transistors and diodes during commutation transients are extracted based on unipolar PWM switching intervals. Contrary to DC-DC converters, the frequency of the switching network (i.e., low-side transistor and high-side freewheeling diode or vice versa in an inverter leg) and the inverter output frequency are different. Thus, in order to be able to extract the equivalent resistance of the inverter switching losses, this paper proposes to use the concept of local and global rms and average currents. The local and global rms currents of the switches are derived in Section III to extract the equivalent averaged resistance of local and global switching power losses based on energy conservation law. The materials described in this section are also beneficial to estimate the averaged equivalent resistance for the conduction power losses of the devices. In Section IV, an output resistance is derived for the CHB inverter using the reflection rule. In Section V, the double-pulse tests (DPT) are conducted on the experimental rig to have an authentic perception of the device switching characteristics for different working conditions. Also, experimental studies are performed on a multilevel CHB to verify the correctness of the inverter's estimated output equivalent resistance. The discrepancies between the experiments and theoretical modeling approach are discussed in Section VI. The paper is concluded by drawing some conclusions in Section VII.

## II. TURN ON AND TURN OFF TRANSIENTS IN THE SWITCHES OF H-BRIDGE INVERTER

The PS-UPWM is commonly used for switching the CHB multilevel converters. A single-phase CHB (SP-CHB) converter with n series-connected HBs, requires n carrier signals, each one time shifted  $T_{cr}/2n$  with respect to the adjacent one, with  $T_{cr}$  being the carrier period, resulting uniform power distribution among HBs and their switches [20]. Assuming that all four transistors in each series-connected HBs carry the same root mean square (rms) current and dissipate the same switching and conduction power losses, only one of the HBs can be considered for the succeeding investigations, as shown in Fig. 1.

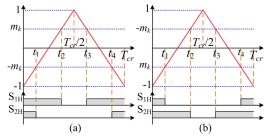

Fig. 1(b) illustrates the mechanism of unipolar PWM in generating switching pulses for HB shown in Fig. 1(a). The reference signal is sampled every half cycle or every cycle of the carrier in double-update-mode or single-update-mode modulators, respectively [20]. As shown in Fig. 2, the switching pulses for the transistors  $S_{1H}$  and  $S_{1L}$  are

Fig. 2. Switching pulses in a period of carrier waveform for (a) m>0 and (b) m<0.

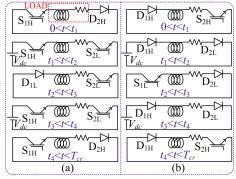

Fig. 3. HB equivalent circuit in the case of m>0 and (a)  $i_o>0$ , and (b)  $i_o<0$ .

generated via comparison of the reference signal  $m\left(t\right)$  with its corresponding carrier signal and those of switches  $S_{2H}$  and  $S_{2L}$  are produced through comparing the carrier with  $-m\left(t\right)$ , being  $m\left(t\right)=M\sin\left(\theta=\omega_{0}t\right)$ , where  $\omega_{0}$  is the electrical pulsations of output voltage and  $M\in\left[0,1\right]$  is the modulation index. The reference has been considered as constant within a period of the carrier in Fig. 2, being the reference frequency almost negligible compared to that of the carrier. The equivalent circuits for the HB are shown in Fig. 3 for the cases of m>0,  $i_{o}>0$  (Fig. 3(a)) and m>0,  $i_{o}<0$  (Fig. 3(b)). In the following, the switching losses are computed for both cases, where the same analysis can be extended to the two other cases, i.e.,  $(m<0,i_{o}>0)$  and  $(m<0,i_{o}<0)$ .

### A. Case m > 0, $i_0 > 0$

As it is obvious from Figs. 2(a) and 3(a), by commanding transistor  $S_{2L}$  at  $t=t_1$ , it turns on and the diode  $D_{2H}$  turns off. Assuming constant load current during the commutation process, i.e.,  $i_o=I_{ok}$ , one can draw the equivalent circuit of Fig. 4 for the HB. In Figs. 5(a) and (b), the approximate (linear) voltage and current waveforms of the transistor are shown for the turn on and turn off transients, respectively. Note that, despite differences such as tail current in the turn off transient of IGBT, the concepts of switching transients are the same for the IGBTs and MOSFETs [21]. This will be explained in more detail in Section II-C.

Based on Fig. 5(a), during the turn on transient, the switch current rises linearly to the load current in a period of  $t_{ri}$ . Then, the voltage across the switch starts to reduce linearly during  $t_{fv}$ . The total delay time, which contributes to the switching losses of the transistor, is  $t_{d,on} = t_{ri} + t_{fv}$ . However, the switch turn on transient is altered in practice due to the diode reverse recovery phenomenon and the displacement

Fig. 4. H-bridge equivalent circuit during the commutation between  $S_{2L}$  and  $D_{2H}$   $(t=t_1)$ .

Fig. 5. Approximate (linear) voltage and current waveforms of switches in HB during (a) transistor turn on, (b) transistor turn off, and (c) transistor turn on considering the diode reverse recovery.

current of the gate-emitter (gate-source in MOSFET) and gate-collector (gate-drain in MOSFET) capacitances [22]. The practical waveform of a switch at turn on is shown in Fig. 5(c). In a real case, when the gate-emitter voltage (or gatesource in MOSFET) exceeds the threshold voltage, the switch current rises and its voltage decreases. The rising interval of transistor current to increase from 0 to  $I_{ok}$  lasts for  $t_{ri}$  during which the diode current falls from  $I_{ok}$  to 0. Within this period, due to the interaction between switch parasitic capacitances and the equivalent inductance seen from the device output capacitance (also called loop inductance), the switch voltage plateaus at a fraction of DC-link voltage until the reverse recovery of the diode is finished [23]. On the other hand, as the diode current reaches zero, the reverse recovery current,  $I_{RR}$ , flows through the diode for an interval of  $t_a$ . This current is added to the transistor current. Hereinafter, the diode is turned off and the voltage across the transistor reduces to nearly zero (saturation region). Note that in Fig. 5(c) usually  $t_{ri} + t_a < t_{d,on} = t_{fv} < t_{ri} + t_{rr}$ .

Thus, according to Fig. 5(c), the currents of  $S_{2L}$  and  $D_{2H}$ , i.e.,  $i_S$  and  $i_D$ , can be expressed by the following equations for the above-mentioned transient

$$i_{S} = \begin{cases} \frac{I_{ok} + I_{RR}}{t_{ri} + t_{a}} t; & 0 \leq t \leq t_{ri} + t_{a} \\ \frac{-I_{RR}}{t_{b}} (t - (t_{ri} + t_{rr})) + I_{ok}; & t_{ri} + t_{a} \leq t \leq t_{ri} + t_{rand} t = t_{4}. \text{ Also, } S_{1L} \text{turns on at } t = t_{2} \text{ and off at } t = t_{3}. \\ \text{Regarding the diodes, } D_{1H} \text{ and } D_{2L} \text{ are turned off at } t = t_{2} \\ I_{ok}; & t \geq t_{ri} + t_{rand} t = t_{4}. \text{ Regarding the diodes, } D_{1H} \text{ and } D_{2L} \text{ are turned off at } t = t_{2} \\ I_{ok}; & t \geq t_{ri} + t_{rand} t = t_{4}. \text{ Also, } S_{1L} \text{ turns on at } t = t_{2} \text{ and off at } t = t_{3}. \\ I_{ok}; & t \geq t_{ri} + t_{rand} t = t_{4}. \text{ Also, } S_{1L} \text{ turns on at } t = t_{2} \text{ and off at } t = t_{3}. \\ I_{ok}; & t \geq t_{ri} + t_{rand} t = t_{4}. \text{ Also, } S_{1L} \text{ turns on at } t = t_{2} \text{ and off at } t = t_{3}. \\ I_{ok}; & t \geq t_{ri} + t_{rand} t = t_{4}. \text{ Also, } S_{1L} \text{ turns on at } t = t_{2} \text{ and off at } t = t_{3}. \\ I_{ok}; & t \geq t_{ri} + t_{rand} t = t_{4}. \text{ Also, } S_{1L} \text{ turns on at } t = t_{2} \text{ and off at } t = t_{3}. \\ I_{ok}; & t \geq t_{ri} + t_{rand} t = t_{4}. \text{ Also, } S_{1L} \text{ turns on at } t = t_{2} \text{ and off at } t = t_{3}. \\ I_{ok}; & t \geq t_{ri} + t_{rand} t = t_{4}. \text{ Also, } S_{1L} \text{ turns on at } t = t_{2} \text{ and off at } t = t_{3}. \\ I_{ok}; & t \geq t_{ri} + t_{rand} t = t_{4}. \text{ Also, } S_{1L} \text{ turns on at } t = t_{2} \text{ and off at } t = t_{3}. \\ I_{ok}; & t \geq t_{ri} + t_{rand} t = t_{4}. \text{ Also, } S_{1L} \text{ turns on at } t = t_{2} \text{ and off at } t = t_{3}. \\ I_{ok}; & t \geq t_{ri} + t_{rand} t = t_{4}. \text{ Also, } S_{1L} \text{ turns on at } t = t_{2} \text{ and off at } t = t_{3}. \\ I_{ok}; & t \geq t_{ri} + t_{ri} +$$

Also, the transistor and diode voltages,  $v_S$  and  $v_D$ , are

$$v_{S} = \frac{-V_{dc}}{t_{fv}} (t - t_{fv}); \quad 0 \le t \le t_{d,on} = t_{fv}$$

$$v_{D} = \begin{cases} 0; & 0 \le t \le t_{ri} + t_{a} \\ -V_{dc}; & t_{ri} + t_{a} \le t \le t_{ri} + t_{rr}, \end{cases}$$

(2)

in which, the switch voltage is approximated by the dashed line in Fig. 5(c).

Consequently, the instantaneous switching losses of the

transistor turn on,  $p_{sw,S,on}$ , and the diode turn off,  $p_{sw,D,off}$ , can be calculated as the product of their voltage and current during the switching transient. Thus,

$$p_{sw,S,on} = v_S i_S; \qquad 0 \le t \le t_{fv}$$

$$p_{sw,D,off} = v_D i_D; \qquad t_{ri} + t_a \le t \le t_{ri} + t_{rr}.$$

(3)

At  $t = t_2$  in Fig. 2(a), transistor  $S_{1H}$  turns off, and based on the load current polarity, diode  $D_{1L}$  turns on. In this regard, diagrams of Fig. 5(b) are drawn for the turn off transient of S<sub>1H</sub>. By removing the command pulse from the transistor,  $v_S$  increases to  $V_{dc}$  during  $t_{rv}$ . Then, the current of  $S_{1H}$ commutates to  $D_{1L}$  during  $t_{fi}$ . The transistor voltage and current equations during the turn off transient are

$$i_{S} = \begin{cases} I_{ok}; & 0 \leq t \leq t_{rv} \\ \frac{-I_{ok}}{t_{fi}} (t - t_{rv}) + I_{ok}; & t_{rv} \leq t \leq t_{rv} + t_{fi} \end{cases}$$

$$v_{S} = \begin{cases} \frac{V_{dc}}{t_{rv}} t; & 0 \leq t \leq t_{rv} \\ V_{dc}; & t_{rv} \leq t \leq t_{rv} + t_{fi}. \end{cases}$$

$$(4)$$

Please note that the voltage spike across the transistor is disregarded in (4) for the sake of simplicity. This will be discussed in detail in Sections II-C and VI. Similar to (3), the instantaneous switching loss of the transistor during turn off interval is  $p_{sw,S,off} = v_S i_S$  for  $0 \le t \le t_{rv} + t_{fi}$ .

According to Figs. 2(a) and 3(a), at  $t = t_3$ , the switch  $S_{1H}$  turns on and  $D_{1L}$  turns off and, consequently, a transient period occurs similar to the one explained for  $t = t_1$ . Also, at  $t = t_4$ ,  $S_{2L}$  turns off and  $D_{2H}$  turns on and the transient period is similar to the one started at  $t = t_2$ . Generally, for calculating the switching power loss for m > 0 and  $i_o > 0$ , one should note that switches S<sub>1H</sub> and S<sub>2L</sub> turn on and turn off once and diodes D<sub>1L</sub> and D<sub>2H</sub> turn off once within a period of carrier waveform, i.e., two switching losses associated with the transistors and diodes in each carrier cycle. This will be later used in Fig. 9 for calculating the output equivalent resistance.

### B. Case m > 0, $i_0 < 0$

Similar to previous explanations in Section II-A, Figs. 2(b) and 3(b) indicate that switch  $S_{2H}$  turns on at  $t = t_1$  and off at  $t = t_4$ . Also,  $S_{1L}$ turns on at  $t = t_2$  and off at  $t = t_3$ .

general, two transistors are turned on and off once and two diodes are turned off once during a switching period just as in the case of m > 0.

### C. Experimental Waveforms of the Switching Transients for IGBT and MOSFET

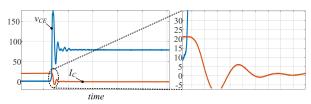

In order to study the differences between the switching characteristics, two HBs with the same PCB layout: one with IGBT [24] and the other with MOSFET [25] were tested. The basic design of the layouts is the same and some minor adjustments were made to optimize the driver circuit. Fig. 6

Fig. 6. Turn off and turn on transients for (a) IGBT ( $V_{CE}$ : collector-emitter voltage,  $I_C$ : collector current,  $I_L$ : inductive load current) and (b) MOSFET ( $V_{DS}$ : drain-source voltage,  $I_D$ : drain current,  $I_L$ : inductive load current).

Fig. 7. Investigating the tail current at turn off for the IGBT under test (no tail current is evident when the device is switched off close to its rated current).

shows the switching transients for both designs. Based on Fig. 6, the switching behavior during these intervals is the same for IGBT and MOSFET and corresponds to the theories presented in Section II-A. Both have voltage oscillations (ringing) across the switch, caused by the interaction between the switch capacitances and loop inductances [23]. The amplitude of the voltage spike and the frequency of oscillations are different for IGBT and MOSFET because of the different rate of change of the switch current and the switch parasitic capacitances. At turn off, the IGBT current falls rapidly first and then with a lower rate during the tailing interval, and depends on component's technology [21]. Typically, in low current applications (e.g., below 50 A), it contributes to a few percent of the turn off loss. The experimental waveforms in Fig. 7 show that the tail current is not very relevant and decays to zero almost linearly. For high-current applications, the tail current is responsible of 15%-20% increase in the turn off losses [26]. In such cases, a piece-wise linear approximation of the current can account for the tail current losses.

## III. EXTRACTING THE EQUIVALENT SWITCHING RESISTANCE BASED ON ENERGY CONSERVATION LAW

There are some works dedicated to the identification of an equivalent resistance for the device switching and conduction losses in DC-DC converters based on the energy conservation law, such as [4] and [27], [28]. In fact, they account for the

TABLE I

CONDUCTING INTERVALS OF SWITCHES

|                    | m > 0               |                                   | m < 0               |                     |  |

|--------------------|---------------------|-----------------------------------|---------------------|---------------------|--|

|                    | i > 0               | i < 0                             | i > 0               | i < 0               |  |

| $0 < t < t_1$      | $S_{1H}, D_{2H}$    | $D_{1H}, S_{2H}$                  | $S_{1H}, D_{2H}$    | $D_{1H}, S_{2H}$    |  |

| $t_1 < t < t_2$    | $S_{1H},S_{2L} \\$  | $D_{1H},D_{2L} \\$                | $D_{1L}, D_{2H} \\$ | $S_{1L}, S_{2H} \\$ |  |

| $t_2 < t < t_3$    | $D_{1L}, S_{2L} \\$ | $S_{1L}, D_{2L} \\$               | $D_{1L}, S_{2L} \\$ | $S_{1L}, D_{2L} \\$ |  |

| $t_3 < t < t_4$    | $S_{1H},S_{2L} \\$  | $\mathrm{D_{1H}},\mathrm{D_{2L}}$ | $D_{1L}, D_{2H} \\$ | $S_{1L}, S_{2H} \\$ |  |

| $t_4 < t < T_{cr}$ | $S_{1H}, D_{2H} \\$ | $D_{1H}, S_{2H} \\$               | $S_{1H}, D_{2H} \\$ | $D_{1H}, S_{2H} \\$ |  |

losses during each switching period in the averaged small-signal model of the converter. Switching frequency in DC-DC converters is the same as the frequency of the switching network output, while these two frequencies are different in an HB. Consequently, to obtain an equivalent resistance representing the device switching and conduction losses in every output period, the concepts of local and global rms values of devices' currents are introduced in this section.

### A. Local and Global rms Currents of the Devices

The "local" (calculated for a period of carrier signal) rms values of the devices' currents can be calculated based on the conduction intervals of switches listed in Table I. Then, the "global" (calculated for a period of output voltage) rms values can be obtained based on the local ones.

Let's consider the output current as  $i_o = I_o \sin{(\omega_o t - \varphi)}$ , with  $I_o$  and  $\varphi$  being the amplitude and the power factor angle of load current, respectively.  $S_{1H}$ ,  $D_{2H}$ ,  $S_{2L}$  and  $D_{1L}$  can conduct when the current is positive, i.e.,  $\varphi < \theta < \varphi + \pi$  (in this interval  $S_{1L}$ ,  $D_{2L}$ ,  $S_{2H}$  and  $D_{1H}$ are constantly off). For  $\varphi < \theta < \pi$ , m and  $i_o$  are both positive and the local rms current of the abovementioned switches can be computed based on Fig. 2(a) and Table I. As in (5),  $t_1$  and  $t_2$  in Fig. 2(a) are obtained by intersecting the equations of both carrier and reference waveforms in the interval of  $0 < t < T_{cr}/2$ .

$$t_1 = \frac{T_{cr}}{4} (1 - m_k); \quad t_2 = \frac{T_{cr}}{4} (1 + m_k).$$

(5)

Accordingly, the local rms values of the currents in  $S_{1H}$ ,  $D_{2H}$ ,  $S_{2L}$ , and  $D_{1L}$  are calculated as in (6) for  $m, i_o > 0$ ,

$$\begin{split} I_{\mathrm{S}_{1\mathrm{H}},rms,k} &= \sqrt{\frac{2}{T_{cr}} \left( \int_{0}^{T_{cr}(1+m_{k})/4} I_{ok}^{2} dt \right)} = I_{ok} \sqrt{(1+m_{k})/2} \, ; \\ I_{\mathrm{S}_{2\mathrm{L}},rms,k} &= \sqrt{\frac{2}{T_{cr}} \left( \int_{T_{cr}(1-m_{k})/4}^{T_{cr}/2} I_{ok}^{2} dt \right)} = I_{ok} \sqrt{(1+m_{k})/2} \, ; \\ I_{\mathrm{D}_{1\mathrm{L}},rms,k} &= \sqrt{\frac{2}{T_{cr}} \left( \int_{T_{cr}(1+m_{k})/4}^{T_{cr}/2} I_{ok}^{2} dt \right)} = I_{ok} \sqrt{(1-m_{k})/2} \, ; \\ I_{\mathrm{D}_{2\mathrm{H}},rms,k} &= \sqrt{\frac{2}{T_{cr}} \left( \int_{0}^{T_{cr}(1-m_{k})/4} I_{ok}^{2} dt \right)} = I_{ok} \sqrt{(1-m_{k})/2} \, . \end{split}$$

For  $\pi < \theta < \pi + \varphi$ , m is negative,  $i_o$  is positive and the local rms current of  $S_{1H}$ ,  $D_{2H}$ ,  $S_{2L}$ , and  $D_{1L}$  can be computed based on Fig. 2(b) and Table I. In this case,  $t_1 = T_{cr} \left(1 + m_k\right)/4$  and  $t_2 = T_{cr} \left(1 - m_k\right)/4$ . Similarly, the devices' local rms currents are obtained in the same manner as the one in (6) and the final expression for the case of m < 0 and  $i_o > 0$  is

$$I_{(S_{1H}, S_{2L}), rms, k} = I_{ok} \sqrt{(1+m_k)/2} I_{(D_{1L}, D_{2H}), rms, k} = I_{ok} \sqrt{(1-m_k)/2}.$$

(7)

Following the same procedure, one can see that the current rms values for  $(S_{1L}, S_{2H})$  and  $(D_{2L}, D_{1H})$  are respectively identical to those of  $(S_{1H}, S_{2L})$  and  $(D_{1L}, D_{2H})$  in (7) for (m > 0, i < 0) and in (6) for (m < 0, i < 0), respectively.

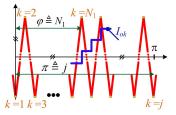

In the next step, the global rms current is calculated. In this paper, the squared local rms values are summed and averaged within an output period and its square root is represented as the global rms current. As mentioned earlier and shown via (6) and (7), local and eventually, global rms currents are the same for all transistors and for all diodes when unipolar modulation is utilized. Hence,  $S_{1H}$  and  $D_{2H}$  are taken as examples for the upcoming calculations. Here, it is assumed that the reference waveform,  $m\left(t\right)$ , and the load current are sampled in every carrier half-period (double-update-mode). Thus, there are j sampling times within a half-period of output voltage,  $T_o$ , as

$$j = \frac{0.5T_o}{0.5T_{cr}} + 1 = \frac{T_o}{T_{cr}} + 1. \tag{8}$$

On the other hand, every switch can conduct either positive or negative load current. Switches  $S_{1H}$  and  $D_{2H}$  can conduct within  $\varphi < \theta < \pi + \varphi$ . Based on double-update-mode sampling strategy and considering the carrier waveform as in Fig. 8, angle  $\varphi$  coincides to the  $N_1$ -th sample equal to  $\lfloor \varphi \times j/\pi \rfloor$ , where  $\lfloor \rfloor$  indicates the floor function. Considering the reference signal as  $m(t) = M \sin{(\omega_o t)}$  and the load current as  $i_o = I_o \sin{(\omega_o t - \varphi)}$ , the global rms current of  $S_{1H}$  and  $D_{2H}$  is obtained based on (6) and (7) as in (9). In fact,  $A_1$ ,  $A_2$ , and  $A_3$  in (9) represent  $I_{ok}$ ,  $(1 + m_k)/2$ , and  $(1 - m_k)/2$  in (6), respectively.

$$\begin{split} I_{S,rms}^{2} &= \left[\frac{\frac{1}{2j}\sum_{k=N_{1}+1}^{j+N_{1}}\underbrace{I_{o}^{2}\sin^{2}\left(\frac{2\pi T_{cr}}{T_{o}}\left(k-1\right)-\frac{N_{1}\pi}{j}\right)}_{A1}\times\right. \\ &\left.\underbrace{\left(\frac{1+M\sin\left(\frac{2\pi T_{cr}}{T_{o}}\left(k-1\right)\right)}{2}\right)}_{A2}\right] \\ I_{D,rms}^{2} &= \left[\frac{\frac{1}{2j}\sum_{k=N_{1}+1}^{j+N_{1}}I_{o}^{2}\sin^{2}\left(\frac{2\pi T_{cr}}{T_{o}}\left(k-1\right)-\frac{N_{1}\pi}{j}\right)}_{A3}\times\right. \\ &\left.\underbrace{\left(\frac{1-M\sin\left(\frac{2\pi T_{cr}}{T_{o}}\left(k-1\right)\right)}{2}\right)}_{A4}\right]. \end{split}$$

In order to check the correctness of the proposed formulation, the rms value of the transistor current is listed in Table II, obtained first from (9) and then from implementing SP-CHB in MATLAB/SIMULINK<sup>®</sup>. In this table, the load rms

Fig. 8. Sampling the reference and load current in double-update-mode.

TABLE II

DEVICES' GLOBAL RMS CURRENTS OBTAINED FROM THEORETICAL

APPROACH AND SIMULATIONS

|             | M           | 0.2   | 0.4   | 0.6   | 0.8   | 1     |

|-------------|-------------|-------|-------|-------|-------|-------|

| $I_{S,rms}$ | Theoretical | 11.43 | 12.03 | 12.82 | 13.45 | 13.97 |

| $I_{S,rms}$ | Simulation  | 11.51 | 12.13 | 12.9  | 13.51 | 14.12 |

| $I_{D,rms}$ | Theoritical | 9.72  | 8.64  | 7.63  | 6.3   | 4.76  |

| $I_{D,rms}$ | Simulation  | 9.8   | 8.72  | 7.7   | 6.41  | 4.84  |

current, carrier frequency and the power factor angle are fixed at 21 A, 2 kHz, and 20°, respectively, and the modulation index is changing. A good matching is observable between the theoretical and simulation results even with relatively low sampling rate (2 kHz). Obviously, the precision of the proposed formulation enhances as the switching frequency increases. One important advantage of the proposed formulation is that the device current rating can be simply and promptly determined for different working points, while it takes plenty of time via simulations.

### B. Local and Global Average Switching Power Losses

Using (1)-(4), the "local average switching power losses" of each transistor and diode,  $P_{sw,S,k}$  and  $P_{sw,D,k}$ , are obtained by integrating the instantaneous switching losses,  $p_{sw,S,on}$ ,  $p_{sw,S,off}$ , and  $p_{sw,D,off}$  in a period of carrier,  $T_{cr}$ , as

$$P_{sw,S,k} = \frac{1}{2T_{cr}} I_{ok} V_{dc} \left[ \frac{t_{d,on}}{3} \left( 1 + \frac{I_{RR}}{I_{ok}} \right) + t_{d,off} \right]$$

$$P_{sw,D,k} = \frac{1}{2T} I_{RR} V_{dc} t_b$$

(10)

where,  $t_{d,on} = t_{fv}$  and  $t_{d,off} = t_{fi} + t_{rv}$ . Also, it is assumed that  $t_{d,on} \simeq t_{ri} + t_a$  which is reasonable as will be explained in Section VI-B.  $P_{sw,S,k}$  in (10) is the sum of local average turn off and turn on switching losses. Equation (10) shows that the transistor local average switching losses are dependent on the load current. Consequently, based on energy conservation law, the local average switching losses in transistor and diode can be expressed as the power dissipated in an equivalent resistance [4], [27],  $r_{ew}$  s k and  $r_{ew}$  D k as

resistance [4], [27],

$$r_{sw,S,k}$$

and  $r_{sw,D,k}$  as

$$r_{sw,S,k} = \frac{P_{sw,S,k}}{I_{S,rms,k}^2}; \qquad r_{sw,D,k} = \frac{P_{sw,D,k}}{I_{D,rms,k}^2} \qquad (11)$$

where,  $I_{S,rms,k}$  and  $I_{D,rms,k}$  are defined according to (6) and (7). On the other hand, just as in the case of device rms currents calculations, "global average switching losses" of each device can be defined by summing the local average switching losses in a period of output voltage by replacing  $I_{ok}$  in (10) by  $I_o \sin (2\pi T_{cr} (k-1)/T_o - N_1 \pi/j)$ . Consequently, global average switching power losses of each switch will be as in the following

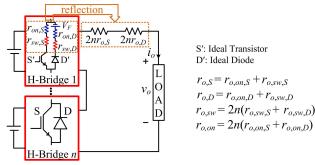

Fig. 9. Representation of devices' equivalent resistances in either series connection to the device or reflected at the inverter output.

$$P_{sw,S} = \frac{1}{2j} \sum_{k=N_1+1}^{j+N_1} P_{sw,S,k} (I_{ok}) P_{sw,D} = \frac{1}{2j} \sum_{k=N_1+1}^{j+N_1} P_{sw,D,k} (I_{ok}).$$

(12)

Similar to the approach utilized for the extraction of local equivalent resistance, the device global equivalent average switching losses resistance, i.e.,  $r_{sw,S}$  and  $r_{sw,D}$ , can be obtained based on energy conservation law as

$$r_{sw,S} = \frac{P_{sw,S}}{I_{S,rms}^2}; \quad r_{sw,D} = \frac{P_{sw,D}}{I_{D,rms}^2}$$

(13)

where the expressions for  $I_{S,rms}$  and  $I_{D,rms}$  are obtained from (9). Hence, these equivalent resistances can be connected in series with each switch model representing its switching power losses as shown in Fig. 9.

## C. Equivalent Averaged Resistance of Conduction Power Losses

The instantaneous conduction power losses of transistors and diodes can be expressed as  $p_{on,S} = r_{on,S}i_S \times i_S$  and  $p_{on,D} = (V_F + r_{on,D}i_D) \times i_D$ , respectively, where  $r_{on,S(D)}$  is the switch on-state resistance and  $V_F$  is the diode threshold voltage. Accordingly, the global averaged conduction power losses,  $P_{on,S(D)}$ , and their equivalent resistances,  $r_{on,S}$  and  $r_{on,D}$ , are calculated as

$$\begin{array}{l} P_{on,S} = \sum_{k} \frac{1}{T_{\rm cr}} \int_{T_{cr}} p_{on,S,k} dt = r_{on,S} I_{S,rms}^2 \\ P_{on,D} = \sum_{k} \frac{1}{T_{cr}} \int_{T_{cr}} p_{on,D,k} dt = r_{on,D} I_{D,rms}^2 + V_F I_{D,rms}. \end{array} \tag{14}$$

## IV. ESTIMATION OF INVERTER OUTPUT SWITCHING AND CONDUCTION AVERAGED RESISTANCES USING REFLECTION RULE

In this paper, the equivalent averaged resistances for switching and conduction power losses in switching devices are extracted. However, these resistances are functions of load power factor, load rms current, and modulation index. Modulation index and power factor are needed to obtain the switching times and the rms current during each period of the carrier and the switching characteristics are required to obtain the local switching power losses. On the other hand, further investigations revealed that the reflected equivalent global resistance to the load branch in Fig. 9 is a function of load rms current, irrespective of power factor and modulation index. In fact, this resistance depends on the voltage and

Fig. 10. Photo of experimental rig for (a) DPT on HB and (b) test on CHB.

the current to be commutated, i.e., dc-link voltage and load current, switching frequency, and the switching characteristics of the device. Consequently, one may arrive at the interesting conclusion that the effect of switching and conduction losses can be modeled by adding equivalent averaged resistances at the inverter output. These conclusions are based on the assumption that the commutating current is continuous in each switching cycle (as it happens in continuous current mode (CCM) in DC-DC converters).

As shown in Fig. 9, the reflection rule can be applied to shift the devices' equivalent averaged resistances to the output terminals of the multilevel CHB. Using the reflection rule, the resistance  $r_x$  in branch 'x' can be shifted to branch 'y' with a resistance of  $r_y$ , where

$$r_{y} = r_{x} I_{x}^{2} / I_{y}^{2}, \tag{15}$$

with  $I_x$  and  $I_y$  being the rms values of currents in branches 'x' and 'y', respectively. In Fig. 9,  $r_{o,S}$  and  $r_{o,D}$  are the transistors' and diodes' reflected resistances to the output, respectively, which, on their own, are the sum of reflected transistor or diode switching,  $r_{o,sw,S(D)}$ , and conduction,  $r_{o,on,S(D)}$ , resistances given by the following equations

$$r_{o,sw,S(D)} = \frac{r_{sw,S(D)}I_{S(D),rms}^{2}}{\left(\frac{I_{o}}{\sqrt{2}}\right)^{2}}; r_{o,on,S} = r_{on,S}I_{S,rms}^{2} .$$

$$r_{o,on,D} = \left(r_{on,D}I_{D,rms}^{2} + V_{F}I_{D,ave}\right)$$

(16)

As shown in Fig. 9, the aforementioned resistances are reflected to the CHB output with a factor 2n for n seriesconnected HBs. This is due to the fact that, in each HB, there are two switching and two conduction power losses associated with transistors and diodes during every switching period.

#### V. EXPERIMENTAL STUDIES

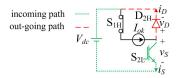

The DPT is utilized to extract the switching characteristics of the device under test (DUT). Then, the device's equivalent switching resistance is obtained based on the proposed method. DPT is a method to extract reliable data of the devices' switching characteristics, that are IGBT turn on and turn off delay times and diode reverse recovery characteristics at different operating conditions [29]- [30]. Two pulses with adjustable duration are sent to the DUT, which is usually the lower switch of an HB phase-leg, in a clamped inductive load circuit. Then, the devices' (IGBT or MOSFET and diode) transients are captured at the end of the first pulse and the beginning of the second pulse.

Since DPT results are very dependent on the circuit layout, one phase-leg of the experimental HB shown in Fig. 10

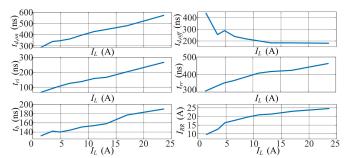

Fig. 11. Switching characteristics of IGBT and diode versus inductive load current,  $I_L$ , in DPT.

was used for accurate estimation. The adopted HB, provided as the whole CHB, by DigiPower Ltd. [31], consisted of NGTB30N120LWG IGBTs and STTH6012W discrete diodes used in snubber circuits [24], [32]. For capturing the transients, a 500 MHz Tektronix MSO58 oscilloscope, 200 MHz Tektronix THDP0200 differential probes, and 120 MHz Tektronix TCP0030A current probes were utilized. The adopted instrumental setup gives satisfactory results for IGBTs as DUT in DPT. According to the device datasheet, the IGBT current rise time  $(t_{rise})$  is up to 200 ns. Hence, the signal bandwidth (BW) would be BW  $\simeq 0.35/t_{rise} \simeq 1.75$  MHz [30]. The minimum BW of the current probe should be three to five times higher than signal BW, which was 120 MHz in our

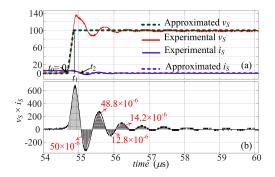

Fig. 6(a) shows a sample of waveforms from DPT to better explain the procedure to extract the switching characteristics, while Fig. 11 shows the DPT results for the IGBT and diode for different current levels. For the purpose of calculating the local switching losses based on (10), the varying switching characteristics for different load (commutation) currents can be stored in a look-up table and utilized in every switching period. This update of switching characteristics is necessary since the load current is sinusoidal and changing.

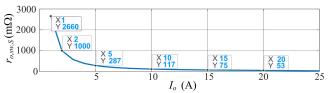

The equivalent global resistance of switching losses,  $r_{sw,S}$ and  $r_{sw,D}$ , of the IGBT and diode is calculated based on the proposed numerical method and listed in Table III and IV for the load rms current of 17 A and different power factor angles and modulation indices. In Tables III and IV,  $(I_o, f_{cr}, V_{dc})$  = (17 Arms, 5 kHz, 500 V). It can be concluded from the results that  $r_{sw,S}$  increases as the power factor and modulation index both decrease, on the contrary,  $r_{sw,D}$ decreases as the power factor and modulation index both decrease. Moreover, the value of output equivalent resistance for switching losses of IGBT and diode, i.e.,  $r_{o,sw,S(D)}$  in (16), is constant for different power factors and modulation indices and are equal to 65.7 m $\Omega$  and 31.3 m $\Omega$ , respectively. It is worth mentioning that the DUT equivalent switching resistance can be obtained quickly based on the proposed numerical method for various working conditions. The equivalent resistance for the switching losses of the experimental seven-level CHB is shown in Fig. 12 for different current levels.

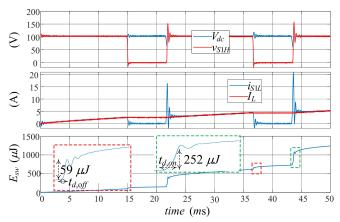

For the purpose of experimental verification, the method presented in [30] and [33] has been also adopted in this paper to verify the local average switching loss of IGBT and diode. In DPT, the difference between the energy drawn from the

TABLE III

EQUIVALENT GLOBAL SWITCHING RESISTANCE IN OHMS FOR IGBT

| M   | $\varphi=0^{\rm o}$ | $\varphi=15^{\rm o}$ | $\varphi=30^{\circ}$ | $\varphi=45^{\circ}$ | $\varphi=60^{\circ}$ |

|-----|---------------------|----------------------|----------------------|----------------------|----------------------|

| 0.1 | 0.243               | 0.244                | 0.246                | 0.249                | 0.253                |

| 0.3 | 0.210               | 0.212                | 0.217                | 0.225                | 0.235                |

| 0.5 | 0.185               | 0.187                | 0.194                | 0.205                | 0.220                |

| 0.9 | 0.149               | 0.152                | 0.160                | 0.173                | 0.194                |

TABLE IV EQUIVALENT GLOBAL SWITCHING RESISTANCE IN OHMS FOR DIODE

| M   | $\varphi=0^\circ$ | $\varphi=15^{\rm o}$ | $\varphi=30^{\circ}$ | $\varphi=45^{\circ}$ | $\varphi=60^{\circ}$ |

|-----|-------------------|----------------------|----------------------|----------------------|----------------------|

| 0.1 | 0.137             | 0.1371               | 0.135                | 0.133                | 0.131                |

| 0.3 | 0.168             | 0.166                | 0.160                | 0.152                | 0.143                |

| 0.5 | 0.218             | 0.211                | 0.196                | 0.176                | 0.157                |

| 0.9 | 0.531             | 0.466                | 0.357                | 0.261                | 0.196                |

power supply and the energy delivered to the inductive load during the switching intervals is equal to the switching losses,  $E_{sw}$ , of IGBT and diode, i.e.,

$$E_{sw} = \int_{0}^{t_d} \left( V_{dc} i_{S_{1L}} - v_{S_{1H}} I_L \right) dt, \tag{17}$$

where,  $i_{\rm S_{1L}}$  and  $v_{\rm S_{1H}}$  are the current of lower switch (DUT) and the voltage of the upper switch (or load) during DPT, respectively. Also,  $t_d$  is the switching time. The energy transfer between the parasitic elements of the circuit (ringing) occurs after the switching interval defined in Fig. 6 and, thus, is not included in (17).

$E_{sw}$  can be computed in the experiments via oscilloscope. For instance, Fig. 13 shows the math operation of (17) on the four channels of the oscilloscope. In this figure the jump of the switching energy in the turn on and turn off transients at the current of 4.6 A and  $V_{dc}=100~{\rm V}$  are equal to  $59+252=311~{\rm \mu J}$ . On the other hand, for the same operating conditions, the local average switching energy, i.e.,  $2T_{cr}~(P_{sw,S,k}+P_{sw,D,k})$  in (10), is computed equal to  $295~{\rm \mu J}$  which is close to the experimental results. Comparisons for other current levels are shown in Table V. According to this table, a good matching can be observed between experiments and the proposed numerical method.

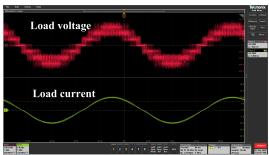

In order to verify the proposed equivalent output resistance for the switching losses, i.e., the term  $r_{o,sw}$  in Fig. 9, experimental studies were carried out using the seven level CHB shown in Fig. 10(b). In the experiments,  $V_{dc}=100~\rm V,~n=3,~f_{cr}=5~\rm kHz$  with PS-UPWM, and M=0.9. Fig. 14 shows the output voltage and current waveforms when the load rms current is 7 A. In Table VI the experimental voltage drops

Fig. 12. Equivalent switching loss resistance of the seven-level CHB.

Fig. 13. Experimental waveforms to obtain the switching loss energy.

TABLE V COMPARISONS BETWEEN NUMERICAL,  $E_{sw,num}$ , and experimental,  $E_{sw,exp}$ , local switching energy loss of IGBT

| $I_L(\mathbf{A})$                       | 2.6  | 3.4 | 4.6  | 7    | 9.5  |

|-----------------------------------------|------|-----|------|------|------|

| $E_{sw,num}\left(\mu \mathbf{J}\right)$ | 184  | 244 | 295  | 379  | 403  |

| $E_{sw,exp}\left(\mu \mathbf{J}\right)$ | 209  | 263 | 311  | 419  | 517  |

| $I_L(\mathbf{A})$                       | 12.7 | 15  | 17.3 | 20   | 23   |

| $E_{sw,num}\left(\mu \mathbf{J}\right)$ | 606  | 741 | 846  | 1008 | 1113 |

| $E_{sw,exp}\left(\mu \mathbf{J}\right)$ | 655  | 769 | 893  | 1041 | 1186 |

with respect to no-load condition,  $\Delta v_{exp}$ , are compared against the presented theoretical ones,  $\Delta v_{th}$ . For the purpose of fair comparison, first the experimental no-load voltage is captured and the fundamental component of this voltage is extracted via FFT analysis of data in MATLAB, which is equal to 185 V for the above mentioned conditions. This should be noted that the dead-time voltage drop, which is a function of  $V_{dc}$ ,  $f_{cr}$ , and  $(T_{dt} + t_{d,on} - t_{d,off})$  [10] is included. Therefore, by neglecting the changes in  $(t_{d,on} - t_{d,off})$  with respect to dead-time duration,  $T_{dt}=2\,\mu s$ , one can assume the dead-time voltage drop as constant for different loading conditions. Table VI shows that the share of switching losses in the voltage drop is comparable to the conduction voltage drops which should be considered. Thus, the proposed modeling of switching losses is useful for appropriate compensation of inverter output voltage drop in some specific applications.

Fig. 14. Output voltage and current of the experimental seven-level SP-CHB.

TABLE VI COMPARISON BETWEEN EXPERIMENTAL AND THEORETICAL VOLTAGE DROPS

| $I_O[A]$ | $r_{o,sw}\left[m\Omega\right]$ | $r_{o,on} \left[ m\Omega \right]$ | $\Delta v_{th} \left[ \mathbf{V} \right]$ | $\Delta v_{exp}\left[\mathbf{V}\right]$ |

|----------|--------------------------------|-----------------------------------|-------------------------------------------|-----------------------------------------|

| 4.8      | 1126                           | 588                               | 8.23                                      | 8.5                                     |

| 7        | 920                            | 500                               | 9.92                                      | 10.8                                    |

| 9.2      | 756                            | 454                               | 11.13                                     | 12                                      |

Fig. 15. Comparison between the analytical model of the transistor at turn off and experimental waveforms, (a) voltage and current, and (b) experimental switching power losses.

## VI. DISCUSSION ON THE DISCREPANCIES BETWEEN THE EXPERIMENTS AND THEORETICAL MODELING

In the real world, the switching waveforms deviate from those presented in Section II-A mainly due to the interaction between the parasitic capacitances of the devices and the loop inductance during switching transients. In the following, the main sources of discrepancies are listed and explained with experimental evidence.

### A. Voltage Spike Across the Switch at Turn off

The transistor experiences a voltage spike when its current reaches zero, which amplitude depends on the rate of change of switch current  $(di_S/dt)$  and loop inductance. An example of the experimental waveforms for the turn off transient is shown in Fig. 15. In this figure, the experimental waveforms are linearized based on the theory presented in Section II-A. The linear equations of the device's current and voltage are

$$v_S = \begin{cases} 0.52 \times 10^9 t; & 0 < t < t_1 \\ 100; & t_1 < t < t_2 \end{cases}$$

$$i_S = \begin{cases} 6.2; & 0 < t < t_1 \\ -193.75 \times 10^6 t + 43.4; & t_1 < t < t_2 \end{cases}$$

(18)

By multiplying the above voltage and current and calculating the integral over  $t_{d,off}$ , the switching energy loss results equal to  $70\,\mu\mathrm{J}$ . Also, this multiplication is done in Fig. 15(b) and the surface area under the instantaneous power loss waveform in the desired period is equal to  $75\,\mu\mathrm{J}$ . It is interesting to note that the error is trivial, despite the relatively large voltage spike. This is due to the fact that the wave tail (after the peak) occurs when the current is zero. Furthermore, the duration of  $(t_2-t_1)$  is short compared to  $t_1$ ,  $32\,ns$  vs.  $192\,ns$  in this case.

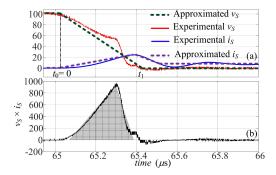

Fig. 16. Comparison between the analytical and experimental waveforms of the transistor at turn on, (a) voltage and current, and (b) experimental switching power losses.

## B. The Linear Approximation of the Switch Voltage and Current at Turn on

Based on Fig. 5(c), the experimental waveforms of the switch's turn on shown in Fig. 16(a) are approximated as in the following equations:

$$v_S = -243.55 \times 10^6 t$$

$+100; 0 < t < t_1 = t_{fv}$

$i_S = 59.42 \times 10^6 t;$   $0 < t < t_1 = t_{fv}$  (19)

It should be mentioned that  $t_{fv} \simeq t_{ri} + t_a$  and there is no need to use the linear approximation of the current for  $t_{ri} + t_a < t < t_{ri} + t_{rr}$ . The switch turn on energy loss is obtained by multiplying voltage and current equations in (19) and taking the integral over  $t_{fv}$  which yields  $167~\mu J$ . The experimental waveform of the instantaneous power loss is also shown in Fig. 16(b) where the surface area under the waveform is nearly  $180~\mu J$ . In general, the sum of theoretical turn on and turn off switching energy loss is equal to  $237~\mu J$  while the experimental one is equal to  $255~\mu J$ . Accordingly, the error introduced by the approximations is around 7%.

### C. Ringing

Ringing is due to the energy exchanges between the input source, parasitic resistances, and the energy storage elements of the circuit, i.e., the switches' parasitic capacitances and loop inductance [33]–[35]. However, in this paper, the main purpose is to extract the converter equivalent resistance based on the average switching power losses. For better clarification, the instantaneous switching power loss during turn off and turn on transients are shown in Figs. 15(b) and 16(b), respectively. The ringing power during turn off takes both negative and positive values which declares the power exchange between energy storage elements of the circuit. In Fig. 15(b), the resultant of energy exchange is negligible compared to the main turn off energy loss. Also, according to Fig. 16(b), the ringing at turn on transient is trivial.

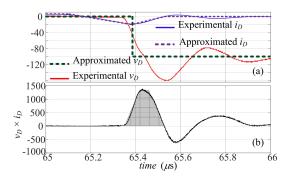

### D. Sudden Change of the Diode Voltage and the Voltage Spike Across the Diode at Turn off

The experimental voltage and current waveforms for the high-side body diode in DPT are shown in Fig. 17 together with the approximated plots, based on the analytical model presented in Section II-A. According to this figure, the real

Fig. 17. Comparison between the analytical and experimental waveforms of the diode, (a) voltage and current, and (b) experimental switching power losses.

diode voltage does not change suddenly but at a very short period and it experiences a spike after reaching the input dc voltage. The approximated equations for the diode voltage and current shown in Fig. 17 are

$$v_S = -243.55 \times 10^6 t$$

+100;  $0 < t < t_1 = t_{fv}$

$i_S = 59.42 \times 10^6 t$ ;  $0 < t < t_1 = t_{fv}$  (20)

By using (20), the approximated diode switching energy loss is equal to  $118\,\mu\mathrm{J}$ . On the other hand, based on Fig. 17(b), the experimental switching energy of the diode is equal to  $133\,\mu\mathrm{J}$ . Thus, the error is nearly 11% which is mainly due to the voltage spike. For a more accurate modeling, the voltage spike can be also considered. This voltage spikes can be extracted from the DPT and applied to the model if more accuracy is needed.

### VII. CONCLUSION

The switching losses of individual devices in HBs depend on modulation strategy, load power factor, switching frequency and devices switching characteristics. In this paper, all these factors have been taken into account and along with a combined theoretical and experimental approach, a switching loss model of the cascaded H-bridge multilevel converter has been obtained. In the theoretical part, the equivalent switching loss resistance of the devices is obtained based on the concept of energy conservation law and through the calculation of local and global switches' rms currents and average switching losses. Then, an output equivalent resistance is obtained based on the reflection rule which is only a factor of load current. The implementation of this theoretical proposal is very effective without the need to extensive simulation studies. In the experimental part, double-pulse test is conducted to obtain the devices' switching characteristics for different switch operating conditions. This modeling approach can be extended to other PWM schemes such bipolar PWM. In other words, the local and global rms values of the device current and switching losses can be obtained based on the specific type of PWM technique similar to the proposed approach.

### ACKNOWLEGMENT

This work was financially supported by Fondo Sociale Europeo – REACT EU – Programma Operativo Nazionale Ricerca e Innovazione 2014-2020 depending on the Ministry of University and Research, MUR-PRIN 2017 Project 2017MS9F49 and by DigiPower srl, 67100 L'Aquila, Italy.

### REFERENCES

- [1] S. M. Seyyedzadeh, S. Mohamadian, M. Siami, and A. Shoulaie, "Modeling of the nonlinear characteristics of voltage source inverters for motor self-commissioning," *IEEE Trans. Power Electron.*, vol. 34, no.12, pp. 12154-12164, Dec. 2019.

- [2] S. M. Seyyedzadeh and A. Shoulaie, "Accurate modeling of the nonlinear characteristic of voltage source inverter for better performance in near zero currents," *IEEE Trans. Ind. Electron.*, vol. 66, no. 1, pp. 71-78, Jan. 2019.

- [3] Y. Park and S. K. Sul, "A novel method utilizing trapezoidal voltage to compensate for inverter nonlinearity," *IEEE Trans. Power Electron.*, vol. 27, no. 12, pp. 4837–4846, Dec. 2012.

- [4] A. Ayachit and M. K. Kazimierczuk, "Averaged small-signal model of PWM DC-DC converters in CCM including switching power loss," *IEEE Trans. Circuits and Systems II: Express Briefs*, vol. 66, no. 2, pp. 262-266, Feb. 2019.

- [5] A. Babel, A. Muetze, R. Seebacher, K. Krischan, and G. Strangas, "Inverter device nonlinearity characterization technique for use in a motor drive system," *IEEE Trans. Ind. Appl.*, vol. 51, no. 3, pp. 2331–2339, May/Jun. 2015.

- [6] H. S. Kim, Y. C. Kwon, S. J. Chee, and S. K. Sul, "Analysis and compensation of inverter nonlinearity for three-level T-type inverter," *IEEE Trans. Power Electron.*, vol. 32, no. 6, pp. 4970-4980, Jun. 2017.

- [7] S. Mohamadian and H. Azizi-Moghaddam, "Conduction and dead-time voltage drops estimation of asymmetric cascaded H-bridge converters utilizing level-shifted PWM scheme," *Iranian Journal of Electrical and Electronic Engineering (IJEEE)*, vol. 16, no. 1, pp. 48-57, Mar. 2020.

- [8] Q. Yan, R. Zhao, X. Yuan, W. Ma, and J. He, "A DSOGI-FLL-based dead-time elimination PWM for three-phase power converters," *IEEE Trans. Power Electron.*, vol. 34, no. 3, pp. 2805-2818, Mar. 2019.

- [9] W. Dafang, Z. Peng, J. Yi, W. Miaoran, L. Gang, and W. Mingyu, "Influences on output distortion in voltage source inverter caused by power devices' parasitic capacitor," *IEEE Trans. Power Electron.*, vol. 33, no. 5, pp. 4261–4273, 2018.

- [10] A. Mora, J. Juliet, A. Santander, and P. Lezana, "Dead-time and semiconductor voltage drop compensation for cascaded H-bridge converters," *IEEE Trans. Ind. Electron.*, vol. 63, no. 12, pp.7833-7842, Dec. 2016.

- [11] S. Ahmed, Z. Shen, P. Mattavelli, D. Boroyevich, and K. Karimi, "Small- signal model of voltage source inverter (VSI) and voltage source converter (VSC) considering the dead-time effect and space vector modulation types," *IEEE Trans. Power Electron.*, vol. 32, no. 6, pp. 4145–4156, Jun. 2017.

- [12] G. S. Perantzakis, F. H. Xepapas and S. N. Manias, "A novel four-level voltage source inverter—influence of switching strategies on the distribution of power losses," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 149-159, Jan. 2007.

- [13] J. W. Kolar, H. Ertl, and F. C. Zach, "Influence of the modulation method on the conduction and switching losses of a PWM converter system," *IEEE Trans. Ind. Applicat.*, vol. 27, no. 6, pp. 1063–1075, Nov./Dec. 1991.

- [14] J. W. Kolar, F. C. Zach, and F. Casanellas, "Losses in PWM inverters using IGBTs," *IEE Proceedings - Electric Power Applicat.*, vol. 142, no. 4, pp. 285-288, Jul. 1995.

- [15] A. M. Hava, R. J. Kerkman, and T. A. Lipo, "Simple analytical and graphical methods for carrier-based PWM-VSI drives," *IEEE Trans. Power Electron.*, vol. 14, no. 1, pp. 49-61, Jan. 1999.

- [16] P. Sanjeev and S. Jain, "Analysis of conduction and switching losses in two level inverter for low power applications," 2013 Annual IEEE India Conference (INDICON), Mumbai, 2013, pp. 1-6.

- [17] G. Ramírez A., M. A. Valenzuela, M. D. Weaver and R. D. Lorenz, "The impact of switching frequency on PWM AC drive efficiency," 2016 IEEE Pulp, Paper & Forest Industries Conference (PPFIC), Austin, TX, 2016, pp. 153-163.

- [18] S. Mukherjee, S. Kumar Giri, S. Kundu and S. Banerjee, "A generalized discontinuous PWM scheme for three-level NPC traction inverter with minimum switching loss for electric vehicles," *IEEE Trans. Ind. Applicat.*, vol. 55, no. 1, pp. 516-528, Jan.-Feb. 2019.

- [19] A. de Paula Dias Queiroz, C. B. Jacobina, A. C. N. Maia, V. F. M. B. Melo, and I. da Silva, "Investigation of a Single-Phase Multilevel Inverter Based on Series/Parallel-Connected H-Bridges," *IEEE Trans. Ind. Applicat.*, vol. 54, no. 5, pp. 4707-4716, Sept.-Oct. 2018.

- [20] M. Malinowski, K. Gopakumar, J. Rodriguez, and M A. Pérez, "A survey on cascaded multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2197-2206, Jul. 2010.

- [21] N. Mohan, T. M. Undeland, and W. P. Robbins, *Power Electronics Converters, Applications, and Designs, 3rd Ed.*, John Wiley & Sons Inc., 2003.

- [22] X. Ye, C. Chen, Y. Wang, G. Zhai, and G. J. Vachtsevanos, "Online condition monitoring of power MOSFET gate oxide degradation based on miller platform voltage," *IEEE Trans. Power Electron.*, vol. 32, no. 6, pp. 4776-4784, Jun. 2017.

- [23] Nexperia AN90011 application note. Half-bridge MOSFET Switch-EMC, 2020. [online] Available: https://assets.nexperia.com/documents/application-note/AN90011.pdf.

- [24] NGTB30N120LWG, available online: https://www.onsemi.com/pdf/datasheet/0l-d.pdf (accessed on 01/10/2022).

- [25] STB120NF10T4, available online at: https://www.st.com/en/power-transistors/stb120nf10t4.html (accessed on 24/01/2023).

- [26] G. Li et al., "A simplified IGBT behavioral model with a tail current module for switching losses estimation," 2017 IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL), Stanford, CA, USA, 2017, pp. 1-6.

- [27] D. Czarkowski and M. K. Kazimierczuk, "Energy-conservation approach to modeling PWM DC-DC converters," *IEEE Trans. Aerospace and Electronic Systems*, vol. 29, no. 3, pp. 1059-1063, Jul. 1993.

- [28] M. K. Kazimierczuk, Pulse-width Modulated DC-DC Power Converters, 2nd Ed, Chichester, UK, John Wiley & Sons, 2016.

- [29] A. Ghosh, C. N. M. Ho, J. Prendergast and Y. Xu, "Conceptual design and demonstration of an automatic system for extracting switching loss and creating data library of power semiconductors," *IEEE Open Journal* of Power Electronics, vol. 1, pp. 431-444, 2020.

- [30] Z. Zhang, B. Guo, F. F. Wang, E. A. Jones, L. M. Tolbert and B. J. Blalock, "Methodology for wide band-gap device dynamic characterization," *IEEE Trans. Power Electron.*, vol. 32, no. 12, pp. 9307-9318, Dec. 2017.

- [31] on line, https://www.digipower.it.

- [32] STTH6012, available online: https://www.st.com/resource/en/datasheet/ stth6012.pdf (accessed on 01/10/2022).

- [33] Zhang, B. Guo and F. Wang, "Evaluation of switching loss contributed by parasitic ringing for fast switching wide band-gap devices," *IEEE Trans. Power Electron.*, vol. 34, no. 9, pp. 9082-9094, Sept. 2019.

- [34] Y. Ren, M. Xu, J. Zhou, and F. C. Lee, "Analytical loss model of power MOSFET," *IEEE Trans. Power Electron.*, vol. 21, no. 2, pp. 310-319, Mar. 2006.

- [35] Z. Zeng, J. Wang, L. Wang, Y. Yu and K. Ou, "Inaccurate switching loss measurement of SiC MOSFET caused by probes: modelization, characterization, and validation," *IEEE Trans. Instrumentation and Mea*surement, vol. 70, pp. 1-14, 2021.

Sobhan Mohamadian (M'22) received his B.Sc. and Ph.D. degrees in Electrical Engineering from Iran University of Science and Technology (IUST), Tehran, Iran, in 2007 and 2016, respectively. Between February 2014 and March 2015, he spent a period as a visiting scholar at the University of Trieste, Trieste, Italy, where he worked on research projects regarding high-power motor drives and multiphase machine modeling and analysis. In 2016, he joined the University of Damghan, Damghan, Iran, where he was an Assistant Professor. From January 2022 he

is working with the University of L'aquila as an Assistant Professor conducting research plans on power electronics converters, renewable energy systems, and electrical machines drives.

Mohammad Modarres received the Ph.D. degree (cum laude) in electrical engineering from the Politecnico di Torino, Turin, Italy, in 2017, where he received the Ph.D. Quality Award from the Department of Electronics and Telecommunications. From 2012 to 2014, he was with the Research Group of Energy Conversion Systems, at Hanyang University, Seoul, South Korea. He was a Post-Doctoral Researcher with the Italian National Measurement Institute of Metrological Research (INRiM), Turin, from 2017 to 2019. Since 2019, he has been working in the

automotive industry on different power electronics converters. His current research interests include power converter designs and electrical motor drives.

Francesco Simonetti (Student Member, IEEE) received his Master Degree in Control Systems and Computer Engineering from the University of L'Aquila, L'Aquila, Italy in 2020. Currently, he is a Ph.D. student at the Department of Information Engineering, Computer Science and Mathematics. His current research interests include optimal control, model predictive control and machine learning techniques applied to power converters and drives with special emphasis on their use with multilevel converters.

Carlo Cecati (Fellow, IEEE) received the Dr. Ing. degree in electrotechnical engineering from the University of L'Aquila, L'Aquila, Italy in 1983. Since then, he has been with the same university where he is a Professor since 2006. From 2015 to 2017, he has been a high-level foreign expert of "Recruitment Program of Global Experts" (1000 Talents Plan) Distinguished Professor with the Harbin Institute of Technology, Harbin, China. His primarily research interests include power electronics, distributed generation, e-transportation and smart grids. Prof. Cecati

has been Co-Editor-in-Chief (2010–2012) and Editor-in-Chief (2013–2015) of the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS. He has been a corecipient of the 2012 and the 2013 Best Paper Award from the IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS, of the 2012 Best Paper Award from the IEEE INDUSTRIAL ELECTRONICS MAGAZINE and of the 2019 Outstanding Paper Award from the IEEE Transactions on Industrial Electronics. In 2017, he received the Antony J. Hornfeck Award from the IEEE Industrial Electronics Society, in 2019 received the title of "Commander of the Republic of Italy" from the President of the Republic of Italy, in 2021 he received the Eugene Mittlemann Achievement Award from the IEEE. He is Chief Technical Officer at DigiPower Ltd., a R&D company active in the field of power electronics.