#### UNIVERSITÀ DEGLI STUDI DELL'AQUILA DIPARTIMENTO DI INGEGNERIA E SCIENZE DELL'INFORMAZIONE

Dottorato di Ricerca in

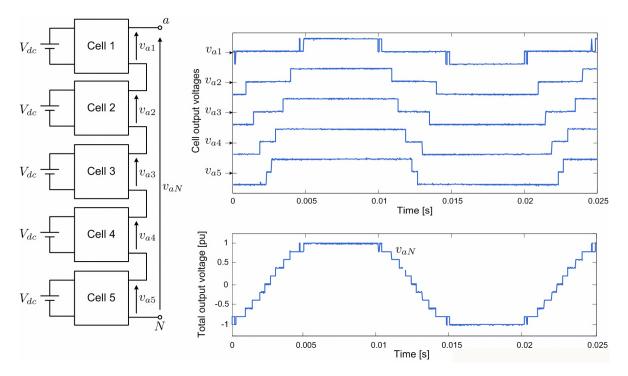

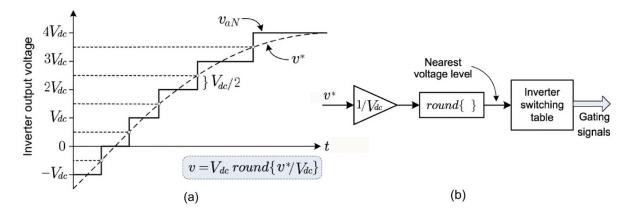

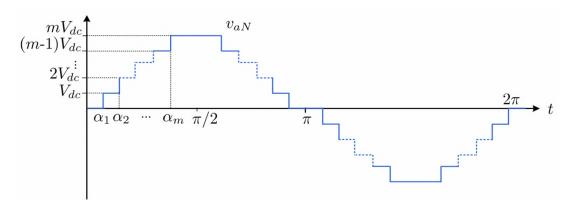

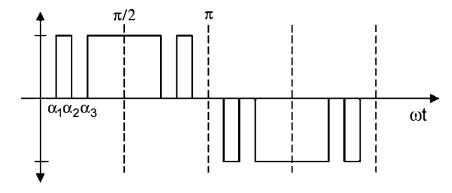

#### INGEGNERIA E SCIENZE DELL'INFORMAZIONE Curriculum: System Engineering, telecommunications and HW/SW platforms

XXXII ciclo

Titolo della tesi

Multilevel Converters: Hardware Design, Advanced Modulation Techniques and Experimental Prototype Validation

SSD ING-IND/32

Dottorando MARIO TINARI

Coordinatore del corso Ch.mo Prof. VITTORIO CORTELLESSA

Tutor CECATI

A.A. 2018/2019

Thesis to get the degree of a Doctor of Philosophy in Information Engineering, Computer Science and Mathematics

# Multilevel Converters: Hardware Design, Advanced Modulation Techniques and Experimental Prototype Validation

Mario Tinari

#### PhD Coordinator

Prof. Vittorio Cortellessa

#### Supervisors

Prof. Carlo Cecati

Prof. Concettina Buccella

Prof. Maria Gabriella Cimoroni

## Acknowledgments

Firstly, I would like to express my sincere gratitude to my supervisor Prof. Carlo Cecati and the co-supervisors Prof. Concettina Buccella and Prof. Maria Gabriella Cimoroni for their continuous guidance and support during my Ph.D. studies.

I must express my very profound gratitude to my family for providing me with unfailing support and continuous encouragement throughout my years of study and through the process of researching and writing this thesis. This accomplishment would not have been possible without them.

A special thanks to my PhD colleagues Vidhi Patel and Ahmed Saif for sharing with me this academic journey and to all the engineers who have collaborated with me at Digipower Ltd. In particular, I would like to express my immense gratitude to Ing. Pietro Ciammaichella for its precious technical teachings and even more for his valuable lessons of humility and kindness.

Last but not the least, I thank all my friends Carlo, Ciro, Francesco, Luca, Nazzareno and Riccardo for their constant support and presence in my life.

Acknowledgments

# Contents

| Ac | know                                                                                            | ledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3                                                         |

|----|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 1  | Abst                                                                                            | tract                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8                                                         |

| 2  | <b>Intro</b><br>2.1<br>2.2<br>2.3                                                               | Description         Background         Outline of Thesis         Related Publications                                                                                                                                                                                                                                                                                                                                                                           | <b>10</b><br>10<br>12<br>13                               |

| 3  | Stat<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                  | e of Art: Multilevel Converter (MLC) Structures          Overview       Overview         Diode-Clamped (Neutral Point Clamped) MLC       Overview         3.2.1       The Main Structure and Conduction States         3.2.2       Characteristics of The NPC multilevel inverters         Capacitor-Clamped (Flying Capacitor) MLC       Overview         Cascaded H-Bridge (CHB) MLC       Overview         Modular Multilevel Converter (MMC)       Overview | <b>15</b><br>15<br>18<br>18<br>19<br>22<br>26<br>31<br>35 |

| 4  | $ \begin{array}{r} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ \end{array} $ | e of Art: Modulation Techniques for Multilevel Converters (MLC)<br>Overview                                                                                                                                                                                                                                                                                                                                                                                     | 58<br>60                                                  |

| 5  |                                                                                                 | vative Modulation Techniques for Multilevel Converters (MLC)         Overview: The power Quality Issue                                                                                                                                                                                                                                                                                                                                                          | <b>69</b>                                                 |

|   | 5.2 | Mixed Harmonic Elimination and Reduction Technique for Single                                                                                                   |    |

|---|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | Phase Nine Level Converters                                                                                                                                     | 72 |

|   |     | 5.2.1 Introduction $\ldots$                                                    | 72 |

|   |     | 5.2.2 Mathematical Model                                                                                                                                        | 72 |

|   |     | 5.2.3 Proposed Procedure                                                                                                                                        | 76 |

|   |     | 5.2.4 Application and Results                                                                                                                                   | 78 |

|   | 5.3 | A High Efficiency Selective Harmonic Elimination Technique for Mul-                                                                                             |    |

|   |     | tilevel Converters                                                                                                                                              | 32 |

|   |     | 5.3.1 Introduction $\ldots$                                                    | 32 |

|   |     | 5.3.2 Mathematical Model                                                                                                                                        | 33 |

|   |     | 5.3.3 Simulation Results                                                                                                                                        | 37 |

|   |     | 5.3.4 Experimental results                                                                                                                                      | 38 |

|   | 5.4 | Single-Phase Chebyshev Algorithm for Harmonics Mitigation in CHB                                                                                                |    |

|   |     | Five-Level Inverters                                                                                                                                            | 39 |

|   |     | 5.4.1 Introduction $\ldots$                                                    | 39 |

|   |     | 5.4.2 Mathematical model $\ldots \ldots \ldots$                      | 39 |

|   |     | 5.4.3 Simulated results                                                                                                                                         | 92 |

|   | 5.5 | Harmonic Elimination Procedure for Cascaded Multilevel Inverters                                                                                                |    |

|   |     | Having a Particular Even Number of DC Sources                                                                                                                   | 95 |

|   |     | 5.5.1 Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                      | 95 |

|   |     | 5.5.2 Mathematical Model                                                                                                                                        | 95 |

|   |     | 5.5.3 Simulation Results $\ldots \ldots \ldots$ |    |

|   |     | 5.5.4 Experimental Results                                                                                                                                      | )2 |

|   | 5.6 | A New Pulse Active Width Modulation (PAWM) for Multilevel Con-                                                                                                  |    |

|   |     | verters                                                                                                                                                         | )4 |

|   |     | 5.6.1 Introduction $\ldots \ldots \ldots$       |    |

|   |     | 5.6.2 Pulse active width modulation (PAWM)                                                                                                                      |    |

|   |     | 5.6.3 Analytical computation of $n$ values that give $V_n = 0$ varying $l = 10$                                                                                 |    |

|   |     | 5.6.4 Comparison with other modulation techniques                                                                                                               |    |

|   |     | 5.6.5 Experimental results                                                                                                                                      |    |

|   |     | 5.6.6 Conclusions $\ldots \ldots 12$                                 |    |

|   | 5.7 | Summary                                                                                                                                                         | 25 |

| 6 | Mai | in Control Board Design 14                                                                                                                                      | 10 |

| - | 6.1 | Overview                                                                                                                                                        | 10 |

|   | 6.2 | Hardware Architecture of the Proposed Multilevel Converter 14                                                                                                   |    |

|   | 6.3 | Architecture of the Main Control Board                                                                                                                          |    |

|   | 6.4 | Main Control Board Characteristics                                                                                                                              | 13 |

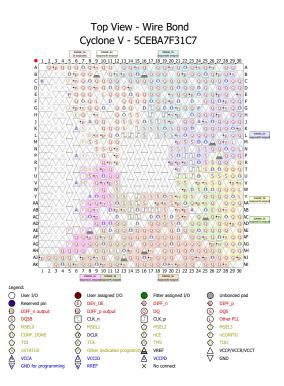

|   |     | 6.4.1 FPGA Device                                                                                                                                               | 14 |

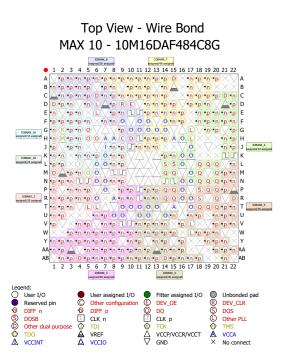

|   |     | 6.4.2 CPLD Device                                                                                                                                               | 14 |

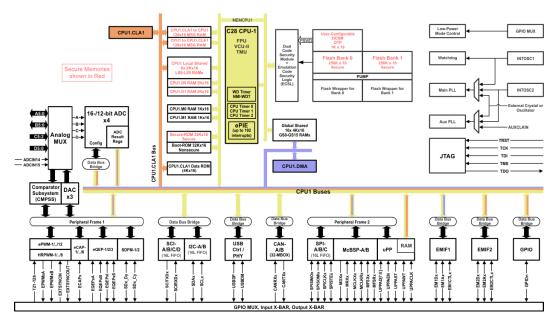

|   |     | 6.4.3 DSP Device                                                                                                                                                |    |

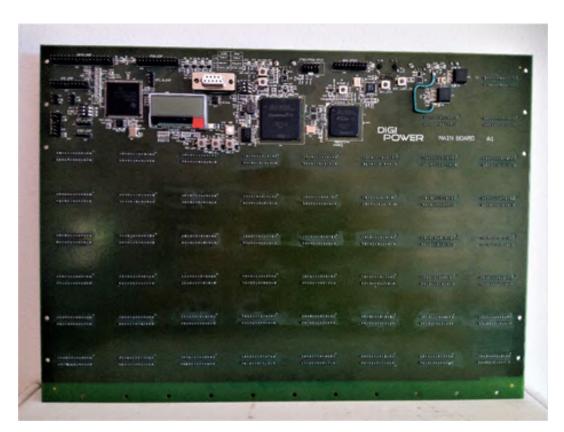

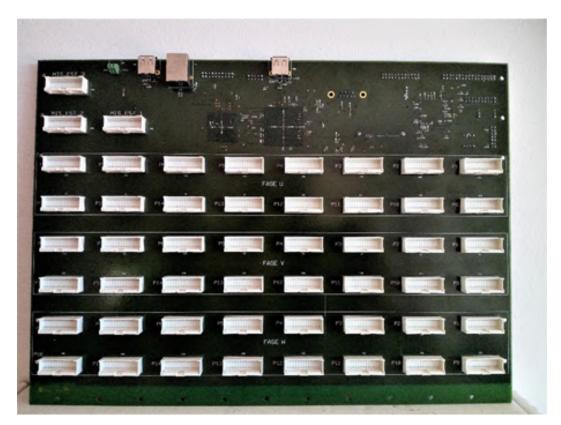

|   | 6.5 | Main Control Board Prototype                                                                                                                                    |    |

|   | 6.6 | Summary $\ldots \ldots 14$                             |    |

|   |     |                                                                                                                                                                 |    |

| 7  | Exp   | erimental Prototype                                     | 152   |

|----|-------|---------------------------------------------------------|-------|

|    | 7.1   | Overview                                                | . 152 |

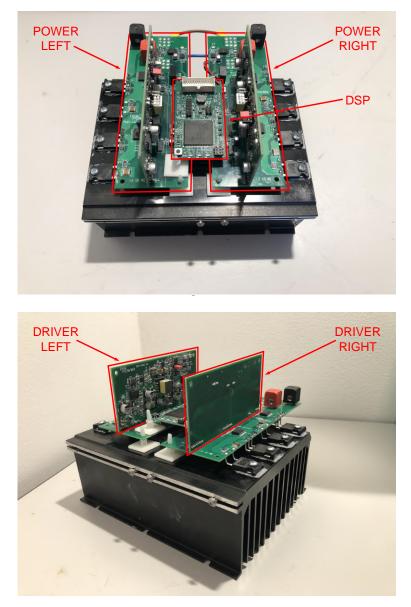

|    | 7.2   | H-bridge Module                                         | . 152 |

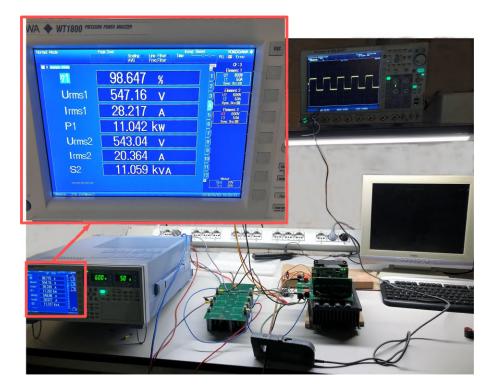

|    |       | 7.2.1 H-bridge Module Power Tests                       | . 156 |

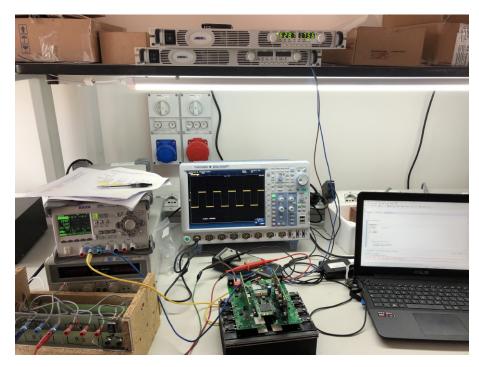

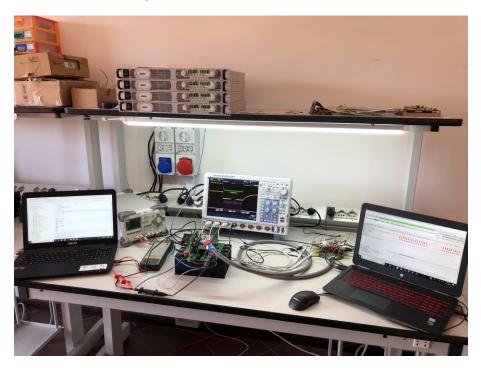

|    | 7.3   | SPI Communication Test                                  | . 158 |

|    | 7.4   | Multilevel Converter Configuration                      | . 160 |

|    | 7.5   | Multilevel Converter Tests                              | . 161 |

|    | 7.6   | Summary                                                 | . 162 |

| 8  | Mu    | tilevel Converter Prototype Applications                | 170   |

|    | 8.1   | D-STATCOM Application                                   | . 170 |

|    |       | 8.1.1 Overview                                          | . 170 |

|    |       | 8.1.2 D-STATCOM Model                                   | . 171 |

|    |       | 8.1.3 Multi-level VSI for D-STATCOM                     | . 173 |

|    |       | 8.1.4 Comparison Between MVSI Topologies for D-STATCOM  | . 174 |

|    |       | 8.1.5 Control Strategies for D-STATCOM                  |       |

|    |       | 8.1.6 Simulation Results                                | . 177 |

|    | 8.2   | Motor Drive Application                                 | . 178 |

|    |       | 8.2.1 Overview                                          | . 178 |

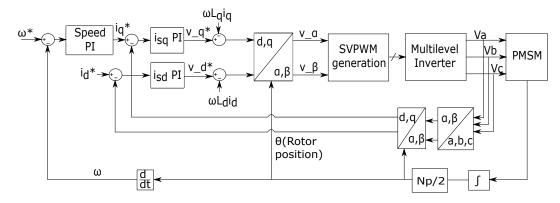

|    | 8.3   | Control of PMSM for EV                                  | . 180 |

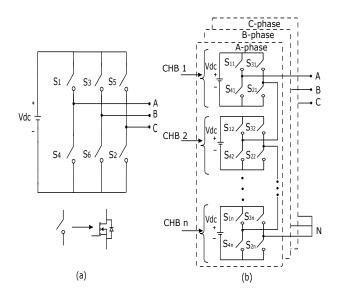

|    | 8.4   | Cascaded H-bridge Multilevel Inverters                  | . 182 |

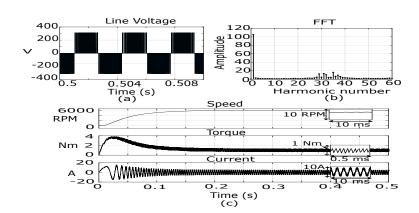

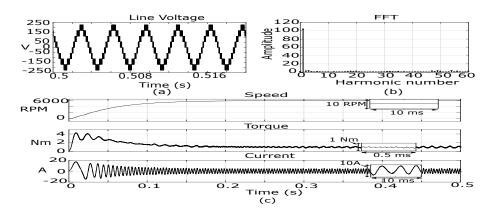

|    | 8.5   | Simulation Results                                      |       |

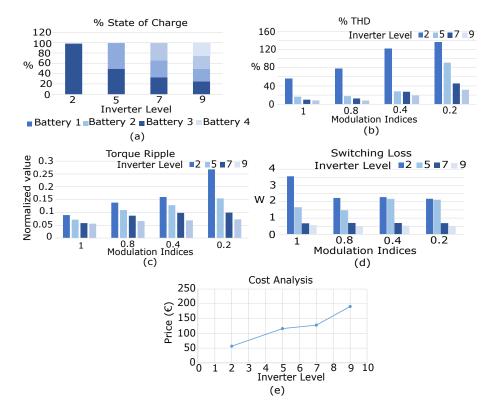

|    | 8.6   | Evaluation of CHB Multilevel Topologies for Power Train | . 187 |

| 9  | Sun   | nmary and Future Work                                   | 190   |

|    | 9.1   | Conclusions                                             | . 190 |

|    | 9.2   | Future Work                                             | . 191 |

| Bi | bliog | raphy                                                   | 193   |

# **List of Figures**

| 3.1  | One phase leg of a two-level inverter and its output voltage $[6]$             | 16              |

|------|--------------------------------------------------------------------------------|-----------------|

| 3.2  | Schematic diagram of one phase leg of MLI for two, three and m levels          |                 |

|      | [6].                                                                           | 17              |

| 3.3  | One phase leg of a three-level NPC with conduction states [6]                  | 20              |

| 3.4  | One phase leg of a five-level NPC and its output voltage [6]                   | 21              |

| 3.5  | The fundamental building block of one phase-leg of a three-level FC            |                 |

| 0.0  | inverter $[6]$ .                                                               | 23              |

| 3.6  | One phase-leg of a three-level FC inverter and conduction states[6].           | 24              |

| 3.7  | Generating of a zero level in FC inverter output voltage $v_{aN}$ and          | <u>م</u> ۲      |

| 20   | conduction states [6]                                                          | $25 \\ 27$      |

| 3.8  | Five-level capacitor-clamped multilevel inverter circuit topology.             | 21              |

| 3.9  | H-bridge inverter, the fundamental cell of cascaded multilevel inverter<br>[6] | 29              |

| 3.11 |                                                                                | $\frac{29}{30}$ |

|      | Diode-based rectifier power cell topologies. (a) Three-phase. (b)              | 00              |

| 0.12 | Single-phase.                                                                  | 31              |

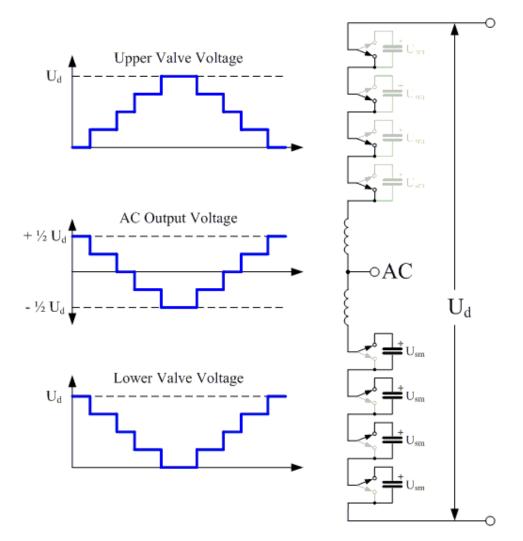

| 3.14 | The operation of MMC valve and phase output voltage.                           | 32              |

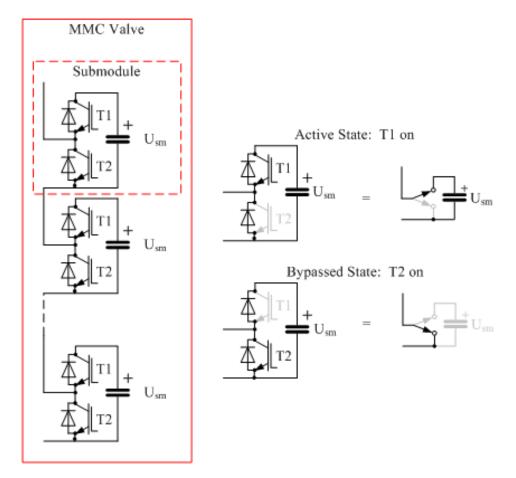

|      | The MMC sub-module (SM) circuit diagram and switching states.                  | 33              |

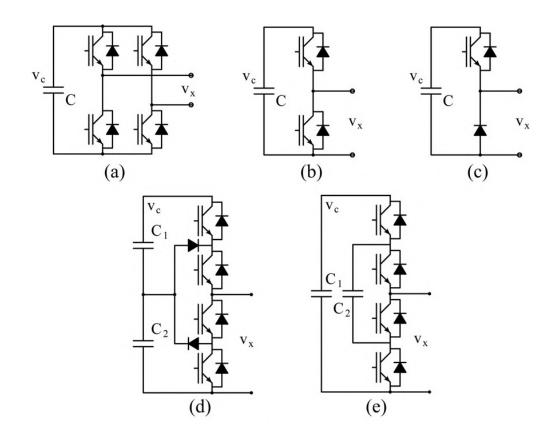

|      | Various power cell topologies for MMC. (a) Full-bridge. (b) Half-              | 00              |

|      | bridge. (c) Unidirectional cell. (d) Multilevel NPC cell. (e) Multilevel       |                 |

|      | flying capacitor cell.                                                         | 35              |

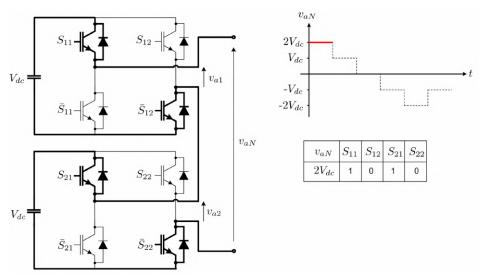

| 3.10 | A 3-level cascaded multilevel inverter and switching states [6]                | 36              |

| 3.13 | The basic structure of Modular Multilevel Inverter (MMC).                      | 37              |

| 3.16 | Three-phase/DC MMC circuit topology for HVDC applications                      | 37              |

| 4.1  | Classification of multilevel converters modulation methods [6]                 | 39              |

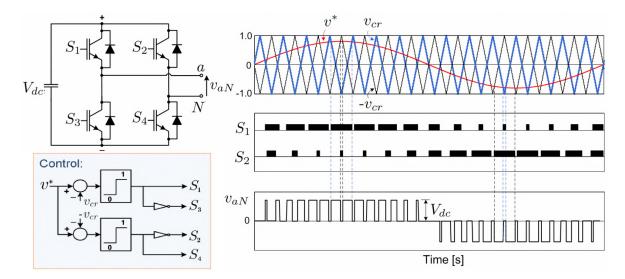

| 4.1  | Bipolar SPWM for a two-level inverter and its control [6]                      | 39<br>41        |

| 4.3  | Unipolar SPWM and its control in a three-level inverter with extra             | 41              |

| 1.0  | phase shifted reference signal [6].                                            | 42              |

| 4.4  | Unipolar SPWM and its control in a three-level inverter with extra             | 12              |

|      | phase shifted carrier signal [6]                                               | 43              |

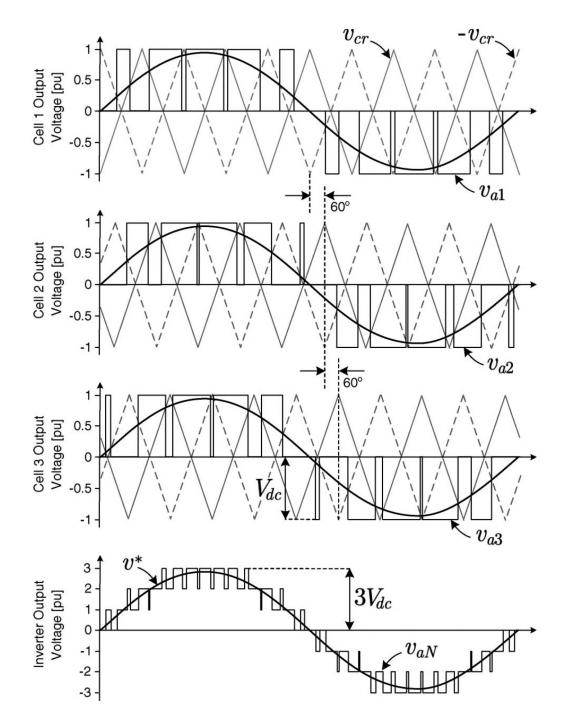

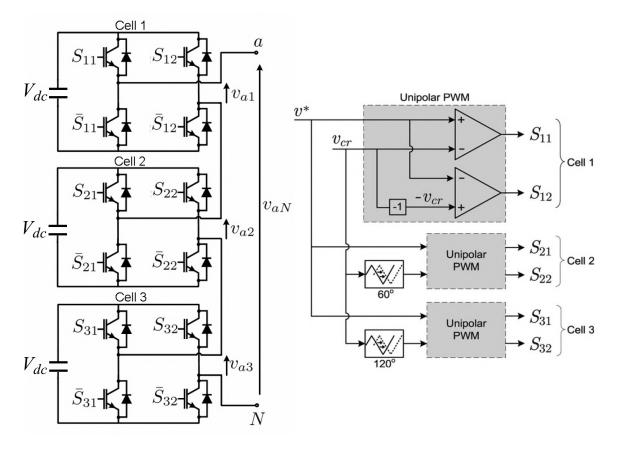

| 4.5  | Three-cell (seven-level) PS-PWM waveform generation for CHB [88].              | 44              |

| 4.6  | Three-cell (seven-level) PS-PWM control diagram for CHB [88].                  | 45              |

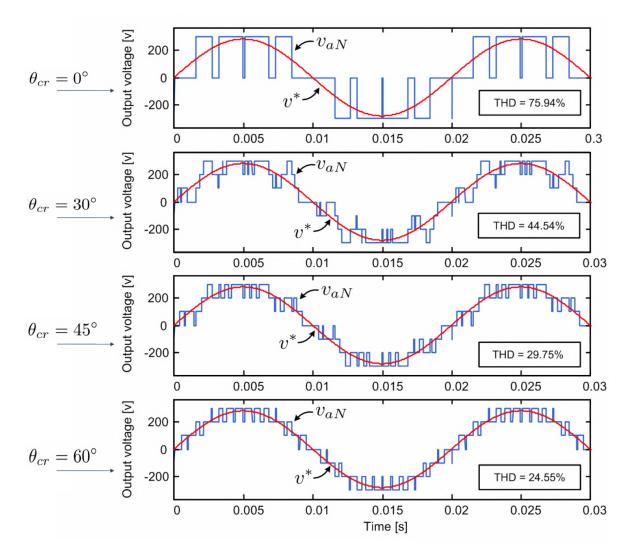

| 4.7  | THD of Three-cell CHB (7-level) PS-PWM for different values of $\theta_{cr}$   |                 |

|      | [6]                                                                            | 46              |

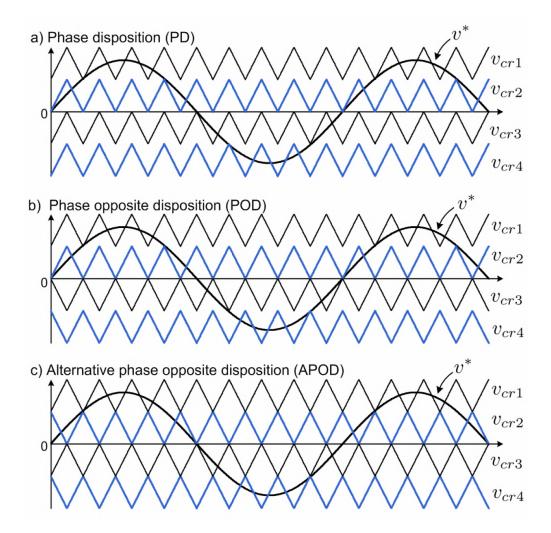

| 4.8  | LS-PWM carrier arrangements: (a) PD, (b) POD, and (c) APOD [88].               | 47              |

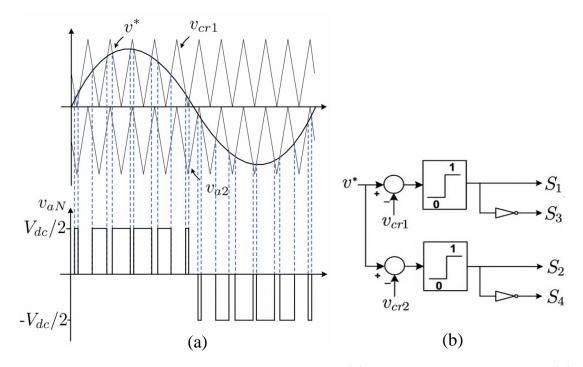

| 4.9     | LSPWM for 3-level NPC inverter: (a) waveform generation and (b)                               |    |

|---------|-----------------------------------------------------------------------------------------------|----|

|         | control diagram (refer to Fig. 3.3) [6]. $\ldots$ $\ldots$ $\ldots$                           | 48 |

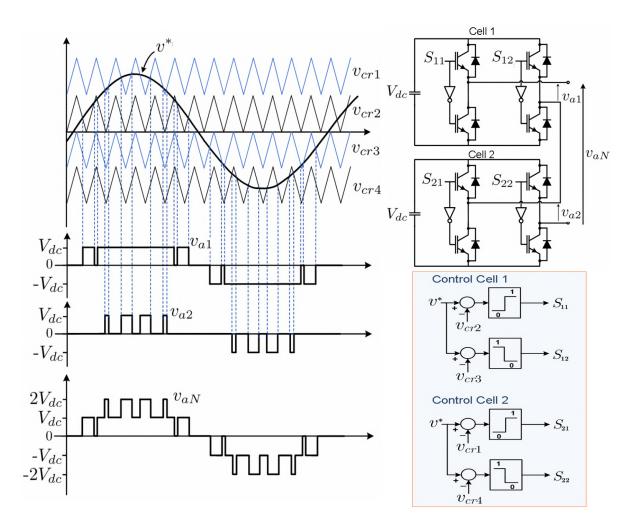

| 4.10    | LS-PWM for 5-level CHB inverter: waveform generation and control                              |    |

|         | diagram [6]                                                                                   | 49 |

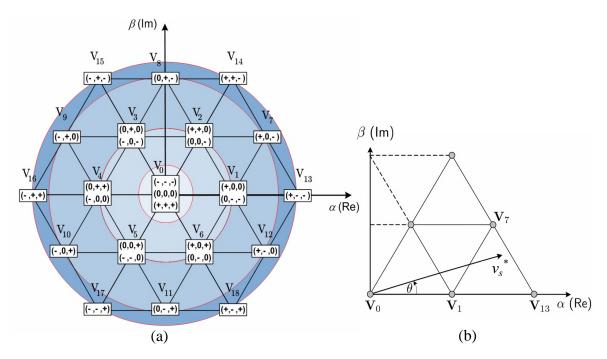

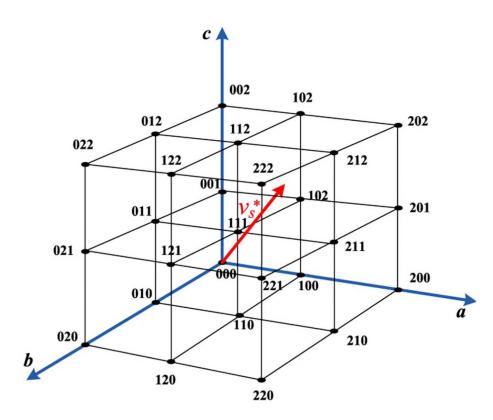

| 4.11    | Space Vector Modulation: (a) Three-phase three-level converter state-                         |    |

|         | space vectors (b) The reference space vector $v_s^*$ mapped in the $\alpha - \beta$           |    |

|         | plane [6]                                                                                     | 52 |

| 4.12    | State-space vectors of a three-phase three-level converter using the                          |    |

|         | 3-D Cartesian coordinates. This control region is plotted using the                           |    |

|         | normalized phase-to-neutral voltages [88]                                                     | 54 |

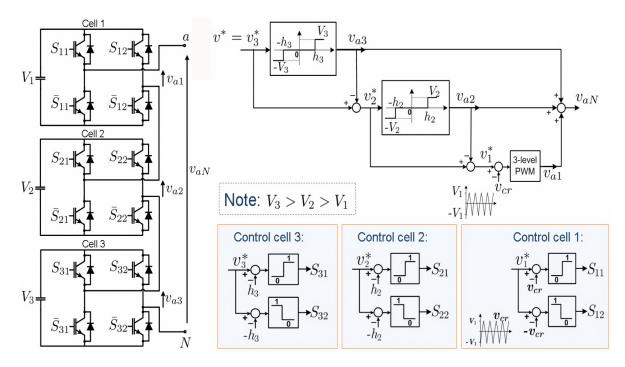

| 4.13    | Hybrid modulation operating principle for 3-cell CHB with unequal                             |    |

|         | dc sources [6]. $\ldots$                                                                      | 56 |

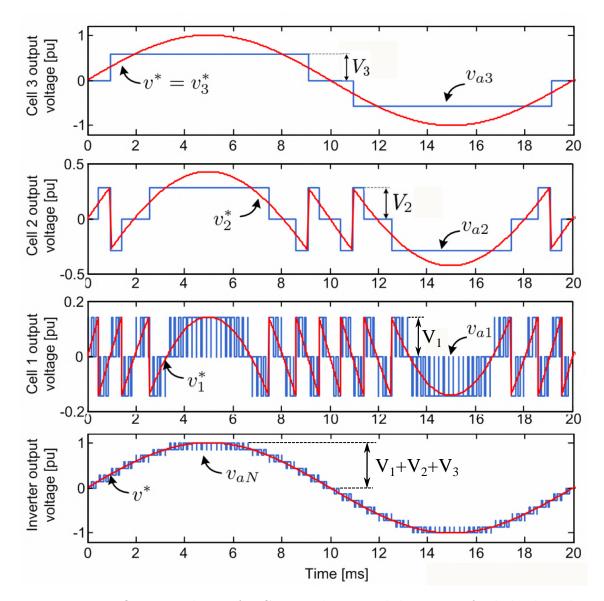

| 4.14    | Output voltages for CHB with unequal dc sources for hybrid modu-                              |    |

|         | lation [6]. $\ldots$                                                                          | 58 |

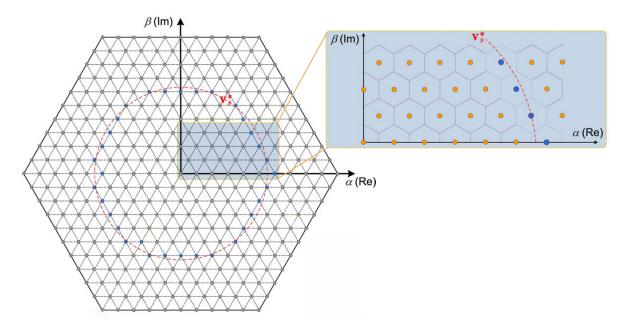

| 4.15    | Multilevel nearest vector control operating principle [6]                                     | 59 |

|         | Voltages generated by an 11-level CHB inverter with NVC [6]                                   | 60 |

|         | Nearest level selection: (a) waveform synthesis and (b) control dia-                          |    |

| 1.1.1   | gram $[88]$ .                                                                                 | 61 |

| 4.18    | Multilevel selective harmonic elimination.                                                    | 64 |

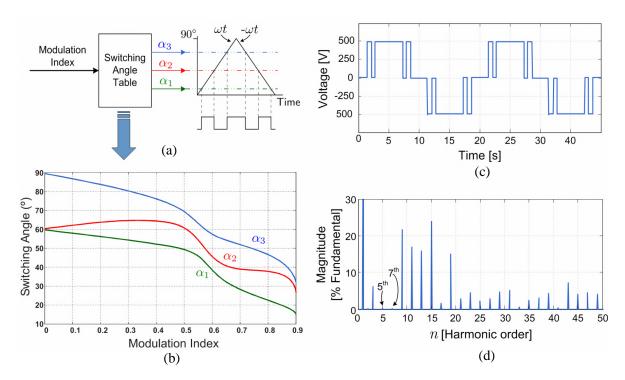

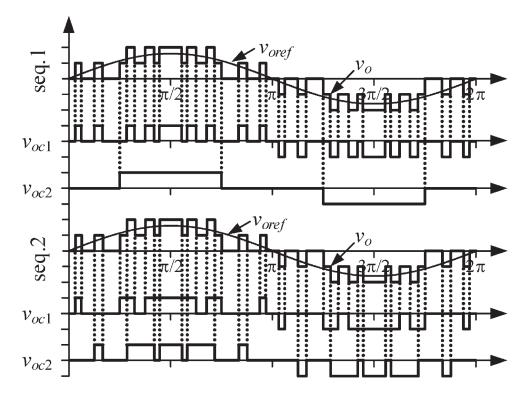

|         | Three-level selective harmonic elimination.                                                   | 64 |

|         | Three-level selective harmonic elimination: (a) implementation dia-                           | 01 |

| 1.20    | gram, (b) angles solution, (c) output voltage, and (d) output voltage                         |    |

|         | spectrum $[6]$                                                                                | 65 |

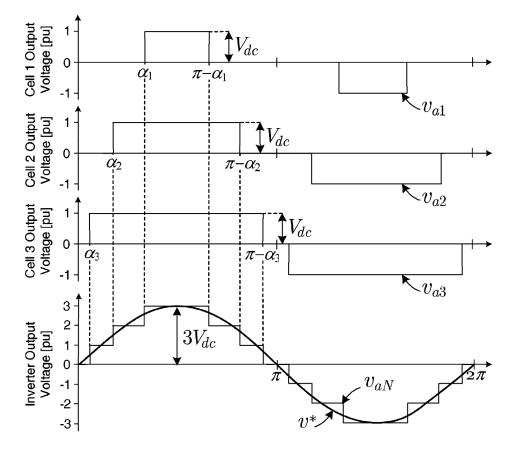

| $4\ 21$ | Seven-level staircase modulation for CHB (One angle per voltage level).                       | 66 |

|         | Five-level SHE technique for CHB (multiple angles per voltage level)                          | 00 |

| 1.22    | [18]                                                                                          | 67 |

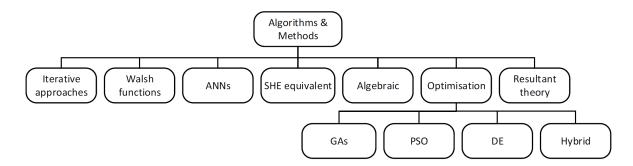

| 4 23    | Classification of SHE-PWM algorithms and solving techniques [76].                             | 68 |

| 1.20    | classification of STEP 1 ((in algorithms and softing teeninques [10].                         | 00 |

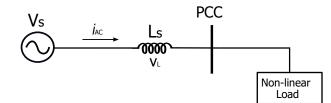

| 5.1     | Single line diagram of power distribution system                                              | 69 |

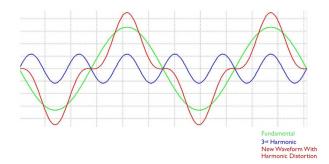

| 5.2     | Harmonic distortion considering only the 3rd harmonic                                         | 70 |

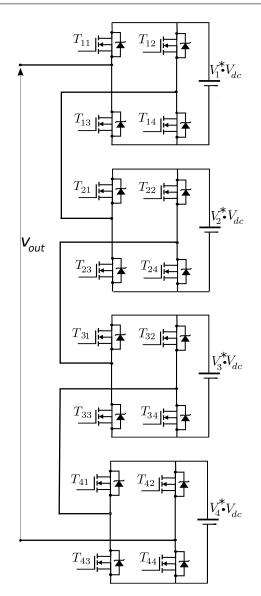

| 5.3     | 9-level single phase inverter.                                                                | 73 |

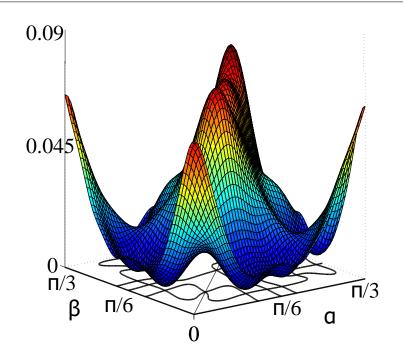

| 5.4     | Surface of equation $(5.16)$ and graphs of the curves $(5.17)$ on the plane                   |    |

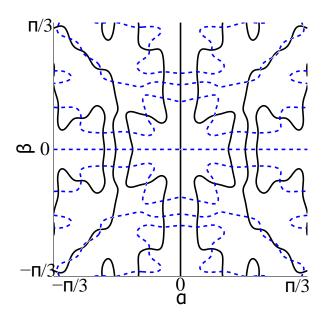

|         | $(\alpha, \beta)$ .                                                                           | 78 |

| 5.5     | Curves $F_1(\alpha, \beta) = 0$ (continuous line) and $F_2(\alpha, \beta) = 0$ (dotted        |    |

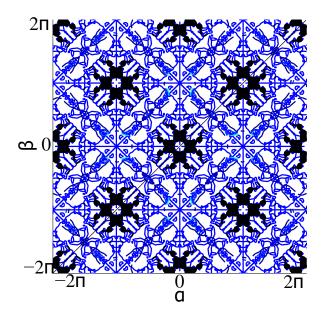

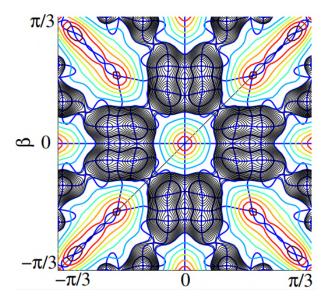

|         | line)                                                                                         | 78 |

| 5.6     | Level curves of equation (5.16) and overlapped to them the curves                             |    |

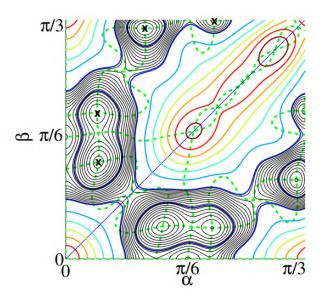

|         | $F_1(\alpha, \beta) = 0$ and $F_2(\alpha, \beta) = 0$ for $\alpha, \beta \in [-2\pi, 2\pi]$ . | 79 |

| 5.7     | Zoom of Fig. Fig. 5.6                                                                         | 79 |

| 5.8     | Zoom of Fig. Fig. 5.7, used for minimum points identifications. Dot-                          |    |

|         | ted lines represent the curves $F_1(\alpha, \beta) = 0$ and $F_2(\alpha, \beta) = 0$          | 80 |

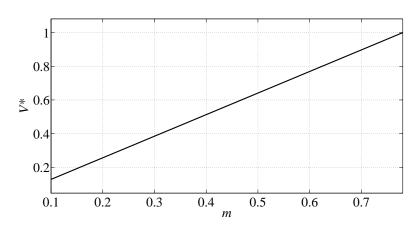

| 5.9     | DC voltage amplitude in p. u.                                                                 | 81 |

| 5.10    | Switching angles producing the minimum <i>THD</i> value                                       | 81 |

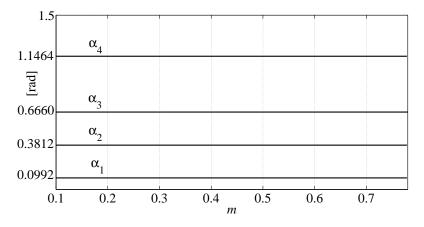

| 5.11    | Block diagram of 9-level inverter with proposed modulation technique                          |    |

|         | and current controlled boost converter                                                        | 82 |

|         |                                                                                               |    |

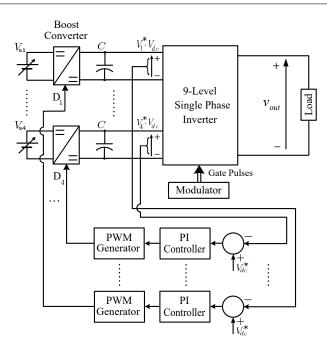

| 5.12 | a) Output voltage waveform, b) Harmonic spectrum.                                   | 84  |

|------|-------------------------------------------------------------------------------------|-----|

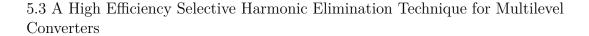

|      | a) DC supply voltage variation, b) Response of the system to DC                     |     |

|      | supply voltage variation.                                                           | 85  |

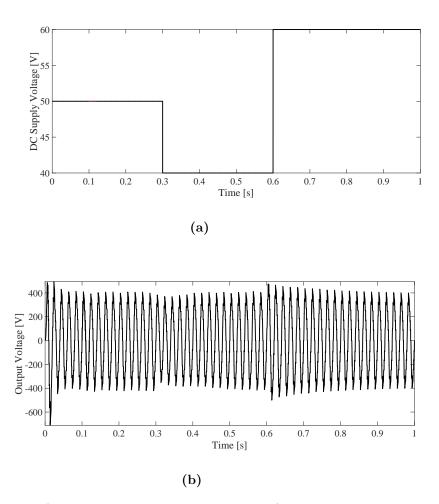

| 5.27 | Cascaded five-level inverter configuration.                                         | 89  |

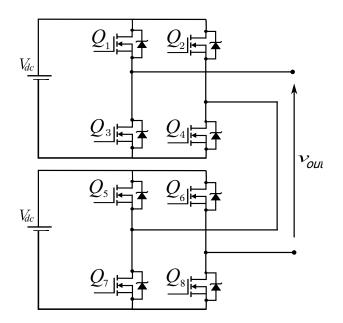

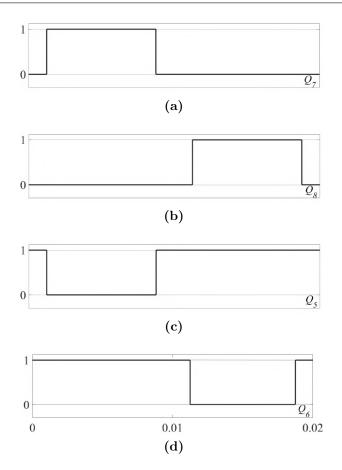

|      | Switching pulses (a) $Q_3$ , (b) $Q_4$ , (c) $Q_1$ , (d) $Q_2$                      | 90  |

|      | Switching pulses (a) $Q_7$ , (b) $Q_8$ , (c) $Q_5$ , (d) $Q_6$ .                    | 91  |

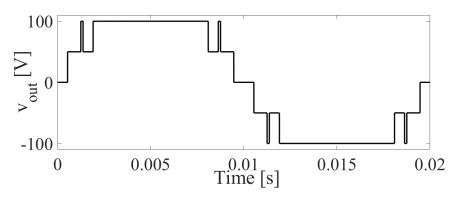

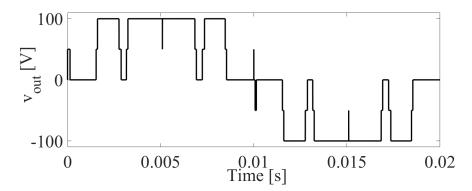

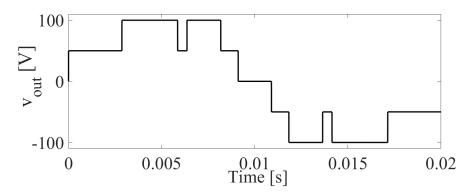

|      | Output voltage waveform obtained by CMT                                             | 92  |

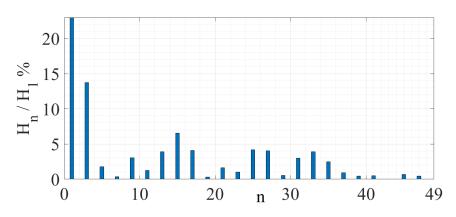

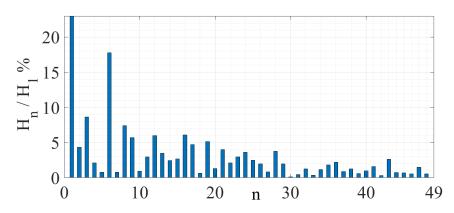

| 5.34 | Harmonic spectrum obtained by CMT                                                   | 93  |

| 5.35 | Output voltage waveform obtained by PSPWM                                           | 93  |

| 5.36 | Harmonic spectrum obtained by PSPWM.                                                | 93  |

| 5.37 | Output voltage waveform obtained by LS-POD-PWM                                      | 94  |

| 5.38 | Harmonic spectrum obtained by LS-POD-PWM                                            | 94  |

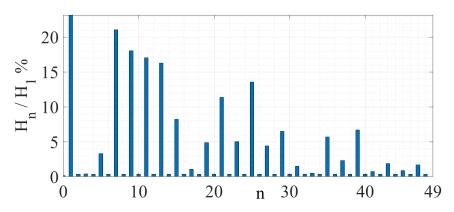

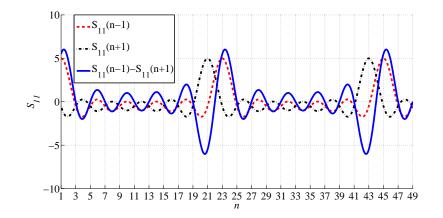

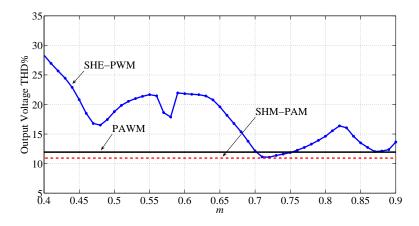

| 5.48 | Behavior of the functions $S_{11}(n-1)$ , $S_{11}(n+1)$ and their difference.       | 111 |

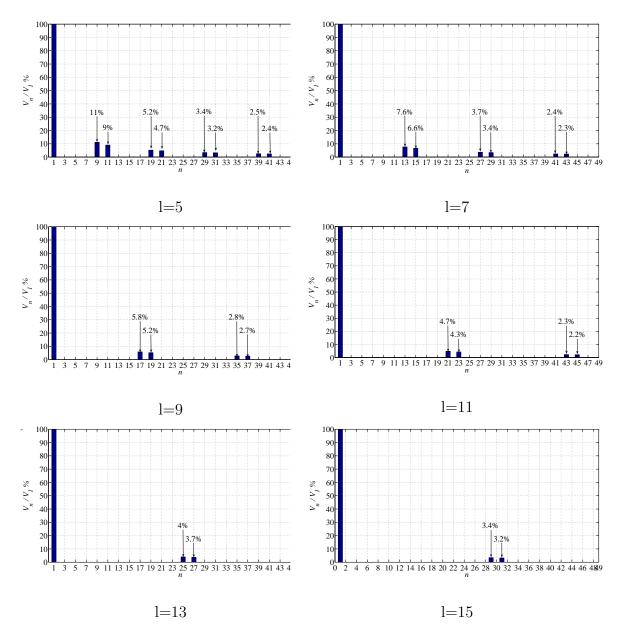

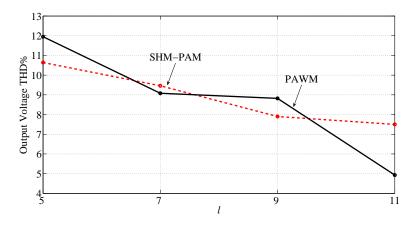

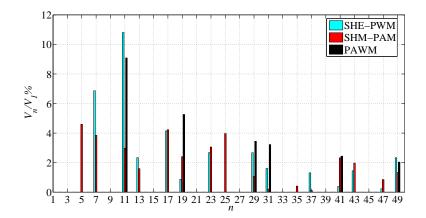

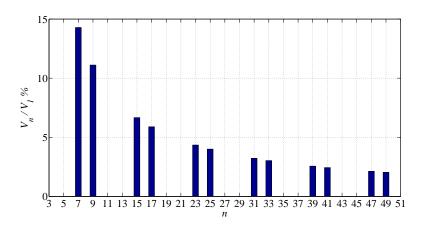

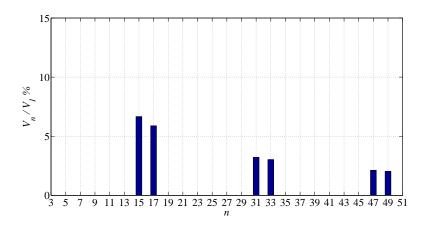

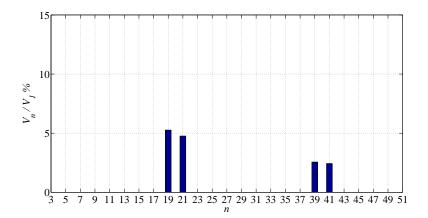

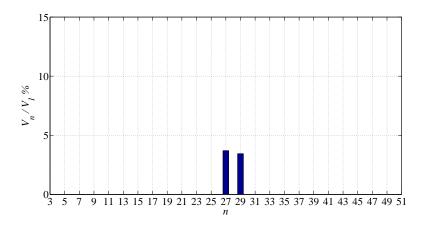

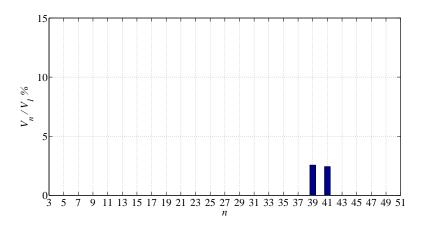

|      | Harmonic analysis obtained for <i>l</i> -level CHB inverters with $l = 5, 7, 9, 11$ |     |

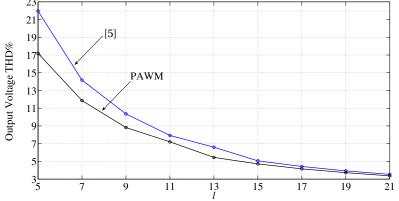

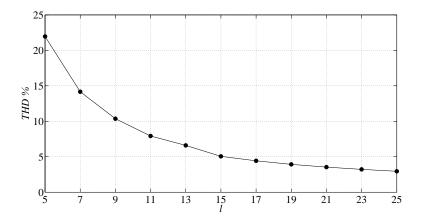

| 5.51 | THD% obtained by PAWM as a function of levels number                                | 115 |

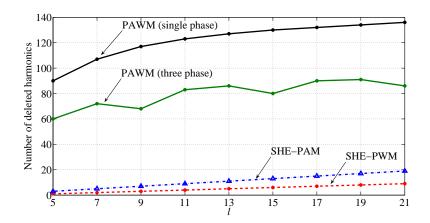

| 5.52 | Number of deleted harmonics as a function of levels number                          | 116 |

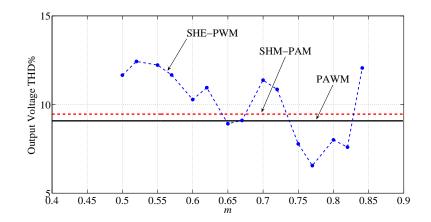

| 5.53 | Output voltage THD% for a three phase CHB 5-level inverter, ob-                     |     |

|      | tained by PAWM and conventional SHE-PWM and SHM-PAM tech-                           |     |

|      | niques                                                                              | 117 |

| 5.54 | Output voltage THD% for a three phase CHB 7-level inverter, ob-                     |     |

|      | tained by PAWM and conventional SHE-PWM and SHM-PAM tech-                           |     |

|      | niques                                                                              | 118 |

| 5.55 | Output voltage THD% for a three phase CHB 5-level inverter, ob-                     |     |

|      | tained by PAWM and conventional SHE-PWM and SHM-PAM tech-                           |     |

|      | niques                                                                              | 118 |

| 5.56 | WTHD for a three phase CHB 5-level inverter, obtained by PAWM,                      |     |

|      | SHE-PWM and SHM-PAM techniques                                                      |     |

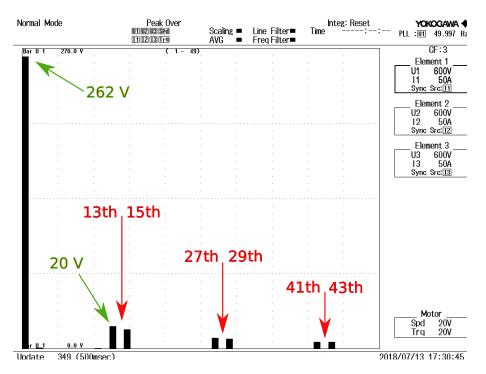

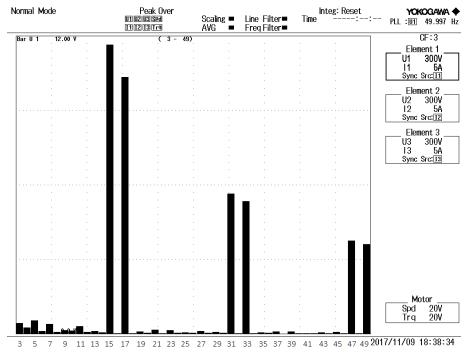

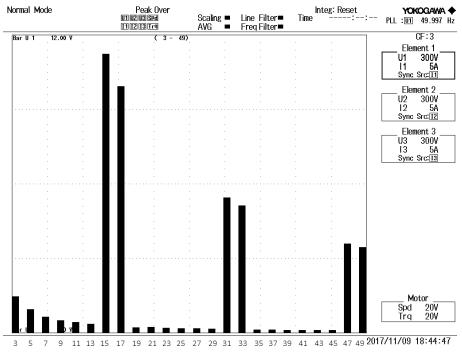

|      | Experimental setup.                                                                 | 120 |

| 5.58 | 5-level inverter configuration: (a) Output voltage (blue line) and cur-             |     |

|      | rent (red line) waveforms, (b) Harmonics amplitudes of output voltage               |     |

|      | in Volt                                                                             |     |

|      | Harmonics amplitudes of output voltage for 7-level inverter                         |     |

|      | Harmonics amplitudes of output voltage for 9-level inverter                         |     |

|      | Harmonics amplitudes of output voltage for 11-level inverter                        |     |

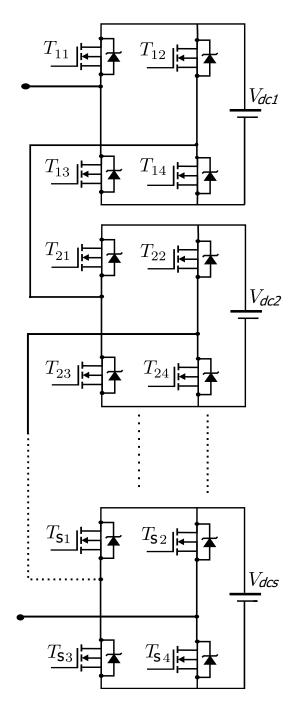

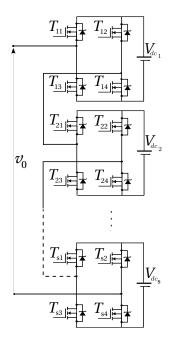

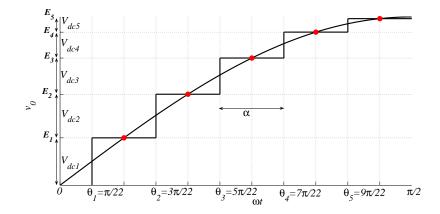

|      | Single-phase <i>l</i> -level inverter configuration.                                |     |

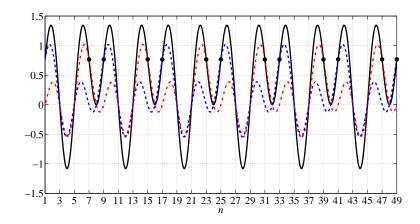

|      | Graphs of formula (5.29) obtained for 5-level inverter                              |     |

|      | Graphs of formula (5.29) obtained for 9-level inverter                              |     |

|      | Graphs of formula (5.29) obtained for 11-level inverter.                            |     |

|      | Spectrum analysis for a 5- level inverter                                           |     |

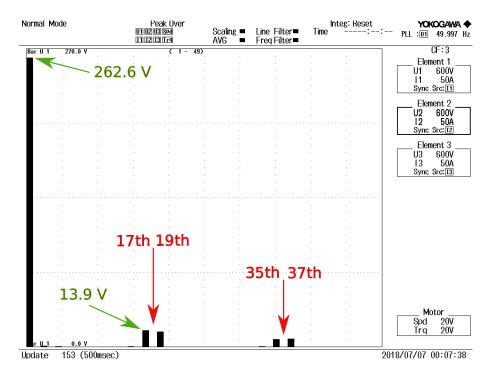

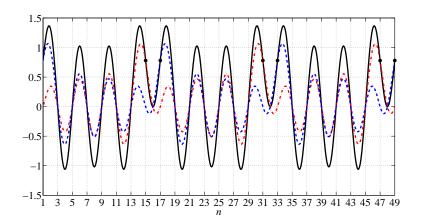

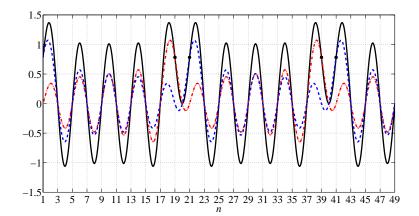

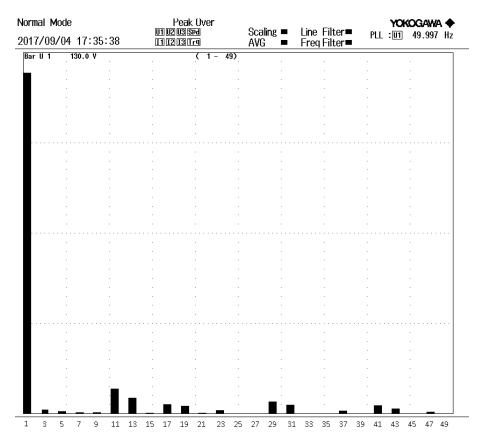

| 5.19 | Spectrum analysis for a 9- level inverter                                           |     |

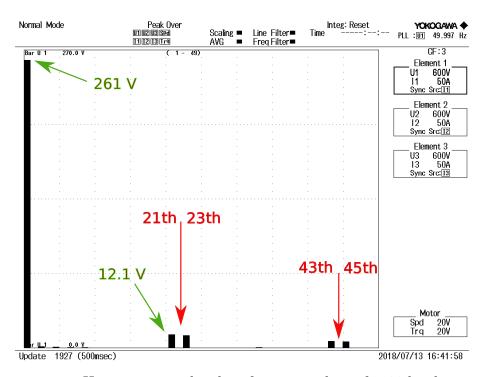

| 5.20 |                                                                                     |     |

|      | Spectrum analysis for a 15- level inverter.                                         |     |

|      | Spectrum analysis for a 21- level inverter.                                         |     |

| 5.23 | THD% depending on number of levels                                                  | 130 |

| 5.24 | Voltage and current waveforms.                                                                   | 131 |

|------|--------------------------------------------------------------------------------------------------|-----|

|      | Harmonic spectrum in open condition.                                                             |     |

|      | Harmonic spectrum in load condition.                                                             |     |

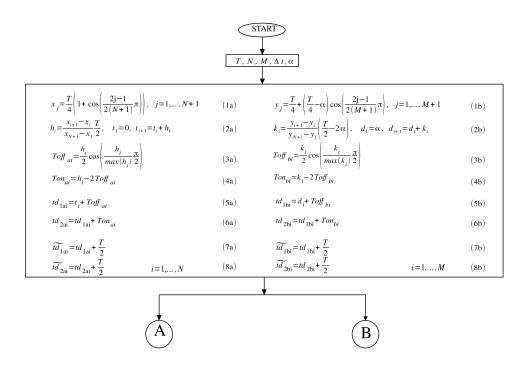

|      | CMT flowchart.                                                                                   |     |

|      | CMT flowchart: (a) part A of Fig. 5.30, (b) part B of Fig. 5.30                                  |     |

|      | Single pulse in $[0, T/2]$                                                                       |     |

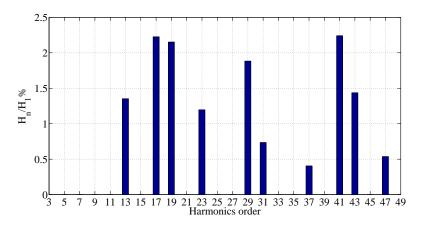

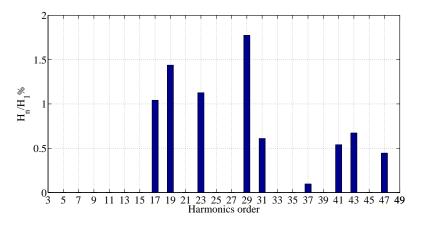

|      | Harmonics amplitude $H_n$ respect to the fundamental H1, for the 5-                              |     |

|      | level inverter.                                                                                  | 134 |

| 5.40 | Harmonics amplitude $H_n$ respect to the fundamental H1, for the 9-                              |     |

| 0.20 | level inverter. $\ldots$                                                                         | 135 |

| 5.41 | Harmonics amplitude $H_n$ respect to the fundamental H1, for the 17-                             | 100 |

| 0.11 | level inverter. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 135 |

| 5.42 | Harmonics amplitude $H_n$ respect to the fundamental H1, for the 33-                             | 100 |

| 0.12 | level inverter.                                                                                  | 135 |

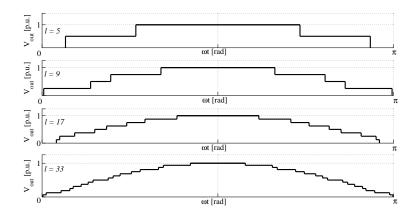

| 5.43 | Output voltages for 5-level, 9-level, 17-level and 33-level inverters                            |     |

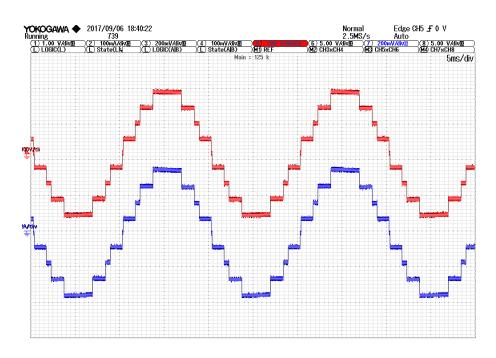

|      | Output voltage and current waveforms                                                             |     |

|      | Harmonic analysis of the output voltage waveform shown in Fig. 5.44.                             |     |

|      | Multilevel inverter configuration.                                                               |     |

|      | 11-level inverter output voltage waveform.                                                       |     |

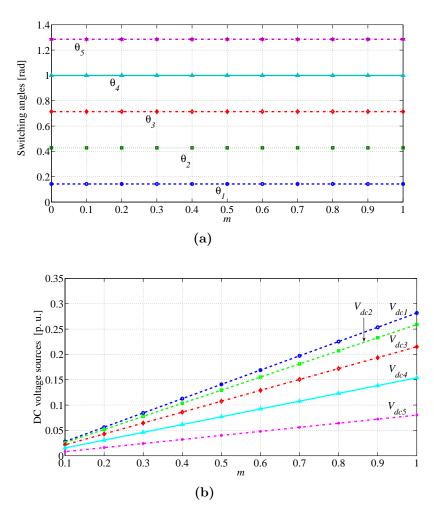

|      | Variation of (a) switching angles and (b) DC voltage sources with $m$                            | 100 |

| 0.49 | in 11-level CHB inverter                                                                         | 128 |

| 5 69 | Transient response.                                                                              |     |

| 0.02 |                                                                                                  | 109 |

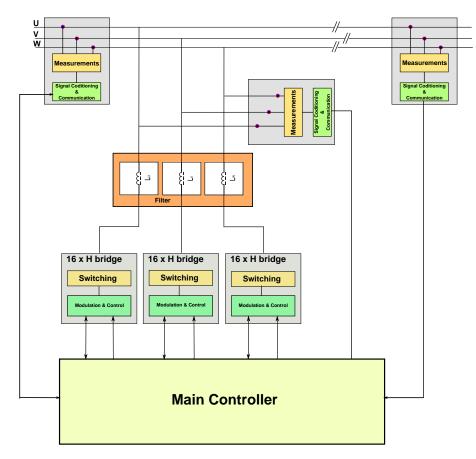

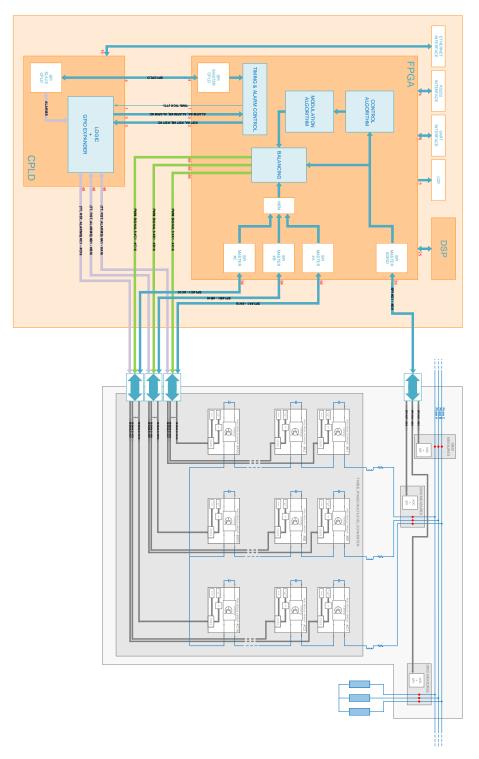

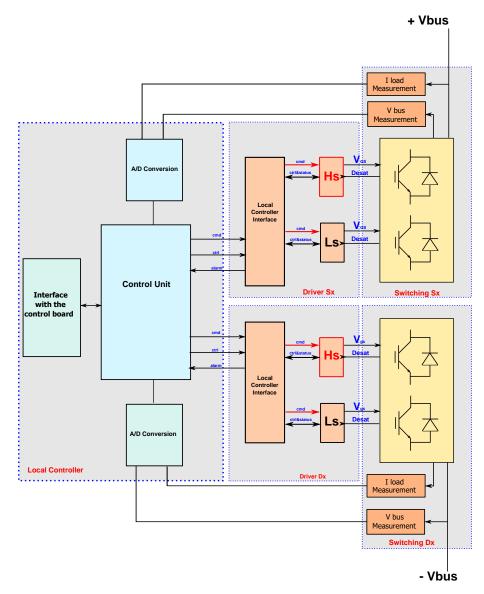

| 6.1  | HW architecture of the system.                                                                   | 142 |

| 6.2  | Block diagram of the main control board                                                          |     |

| 6.3  | Architecture of the system                                                                       |     |

| 6.4  | Detailed architecture of the system                                                              |     |

| 6.5  | Pin planner of CYCLONE V FPGA 5CEFA7F31[329]                                                     |     |

| 6.6  | Pin planner of ALTERA MAX 10 10M16DAF484[329]                                                    |     |

| 6.7  | TMS320F28377S - Functional Diagram [330]                                                         |     |

| 6.8  | Main control board prototype (top view)                                                          |     |

| 6.9  | Main control board prototype (bottom view)                                                       |     |

| 0.0  |                                                                                                  | 101 |

| 7.1  | H-bridge power module.                                                                           | 153 |

| 7.2  | H-bridge module sections. DSP board (on the top), left power leg                                 |     |

|      | (on the left), right power leg (on the right), local DSP board (in the                           |     |

|      | center)                                                                                          | 154 |

| 7.3  | H-bridge schematic functional block.                                                             | 155 |

| 7.4  | Low power test of the H-bridge module.                                                           |     |

| 7.5  | High power test of the H-bridge module.                                                          |     |

| 7.6  | Setup for the SPI Connection test.                                                               |     |

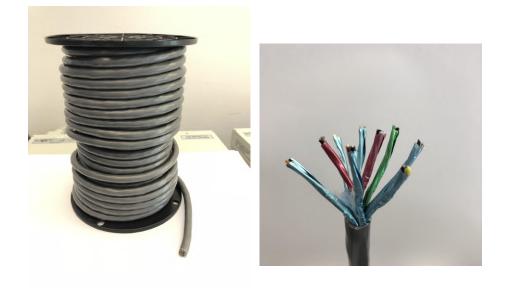

| 7.7  | Cable Belden 9992.                                                                               |     |

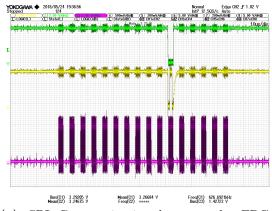

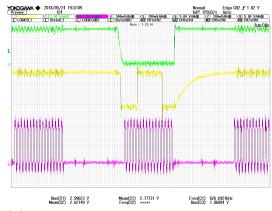

| 7.8  | SPI communication signals                                                                        |     |

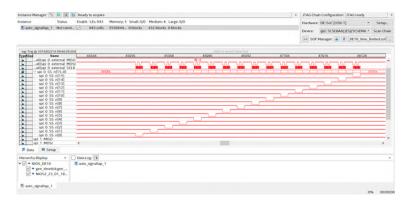

| 7.9  | Signal tap of the FPGA board.                                                                    |     |

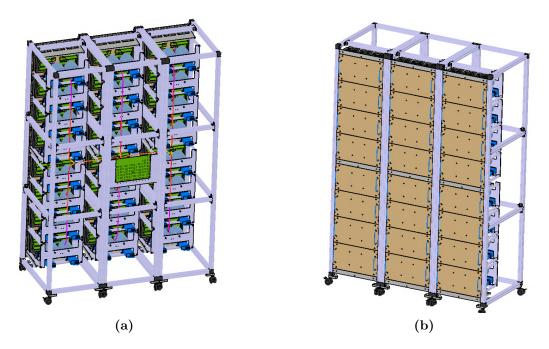

| 7.10 | Project of the racks for the multilevel converter: (a) back view and                                      |

|------|-----------------------------------------------------------------------------------------------------------|

|      | (b) front view. $\ldots$ |

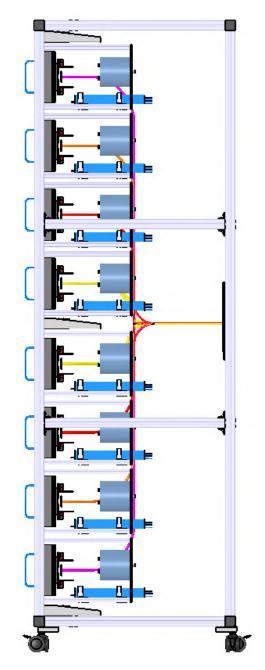

| 7.11 | Project of the racks for the multilevel converter-side view                                               |

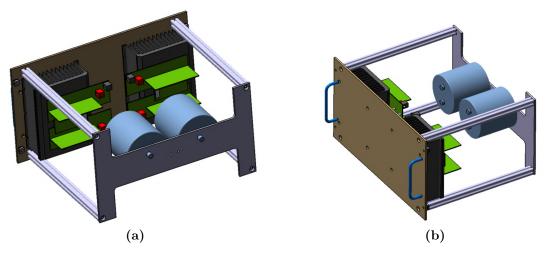

| 7.12 | Project of the drawers: (a) back view and (b) side view                                                   |

| 7.13 |                                                                                                           |

| 7.14 |                                                                                                           |

| 7.15 |                                                                                                           |

| 7.16 |                                                                                                           |

| 7.17 |                                                                                                           |

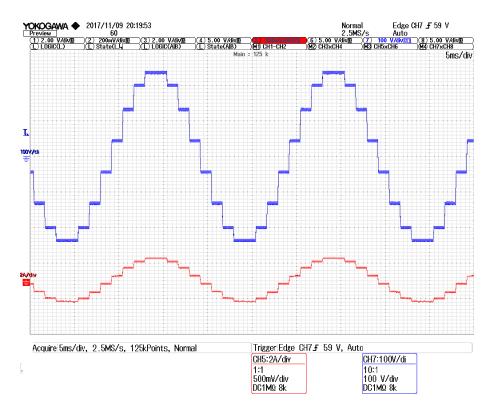

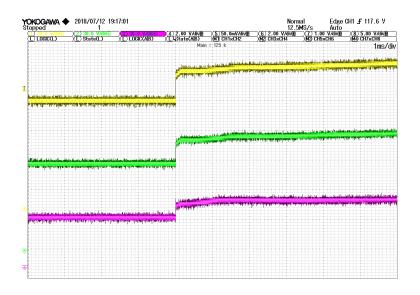

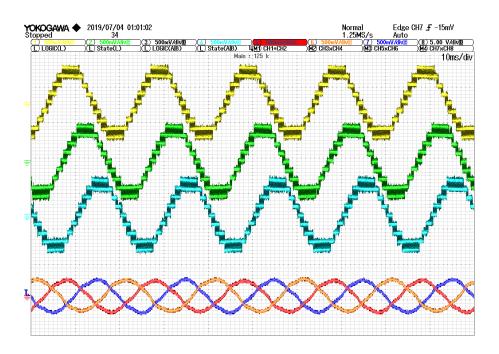

| 7.18 | Voltage and current waveform for a 9 level three-phase configuration                                      |

|      | with multilevel space vector modulation                                                                   |

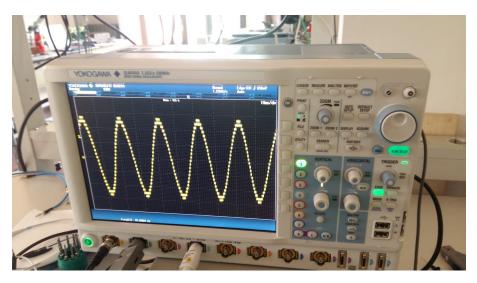

| 7.19 | Voltage output of a 25 level single-phase configuration with phase                                        |

|      | shifted modulation technique                                                                              |

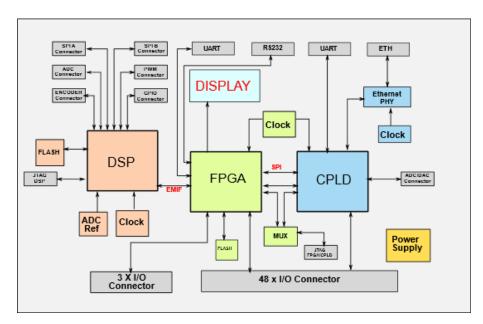

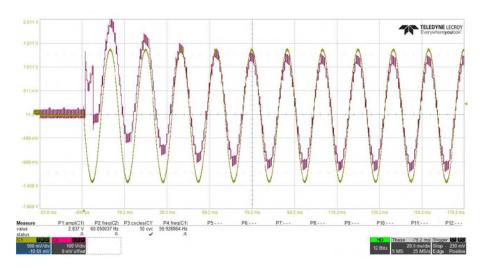

| 7.20 | PLL synchronization test performed in the ENEA research center                                            |

|      | of Portici (NA). In yellow the grid voltage, in purple the multilevel                                     |

|      | output voltage of the converter prototype                                                                 |

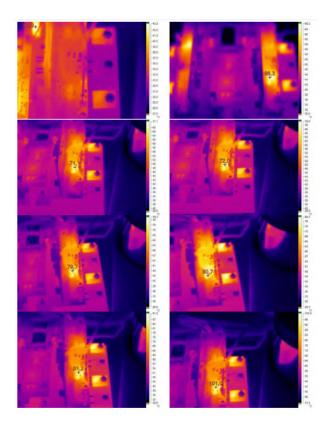

| 7.21 | Thermal tests performed on the single Hbridge module in the ENEA                                          |

|      | research center of Portici (NA)                                                                           |

|      |                                                                                                           |

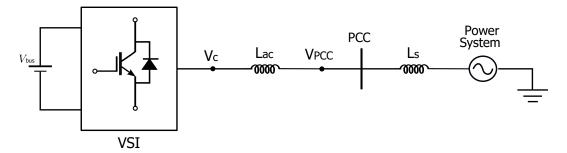

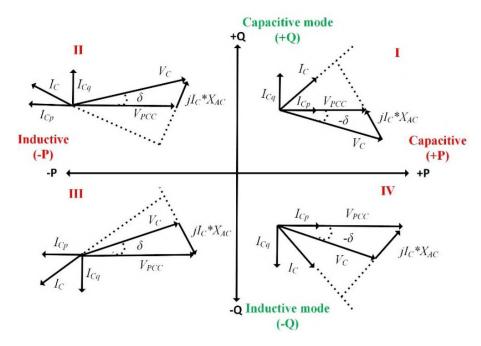

| 8.1  | Single line diagram of D-STATCOM                                                                          |

| 8.2  | Phasor diagram for power exchange in D-STATCOM                                                            |

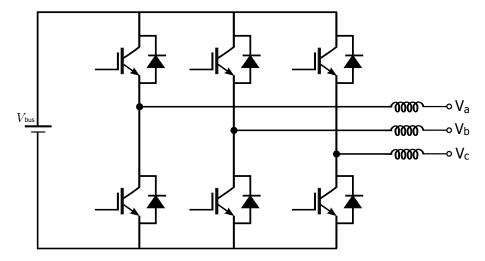

| 8.3  | Three-phase two-level VSI                                                                                 |

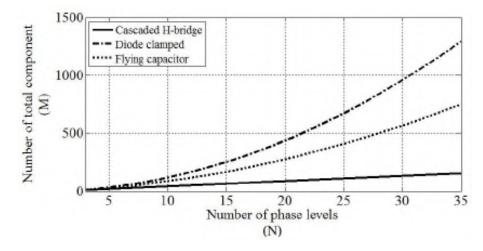

| 8.4  | Total number of components $(M)$ as a function of phase voltage level                                     |

|      | (N) in MVSI [362]                                                                                         |

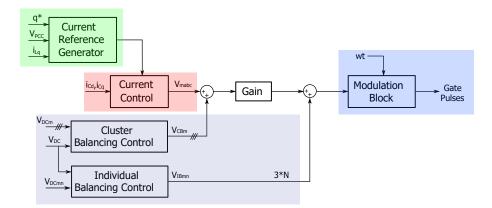

| 8.5  | STATCOM direct control scheme                                                                             |

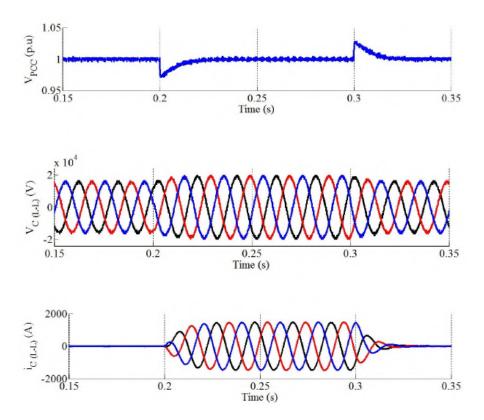

| 8.6  | Performance of the proposed D-STATCOM for sag mitigation 179                                              |

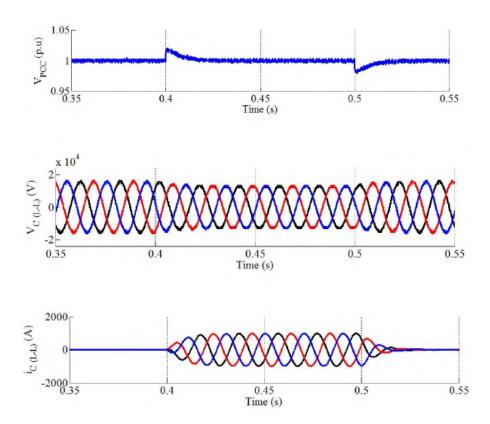

| 8.7  | 4.12: Performance of the proposed D-STATCOM for swell mitigation. 180                                     |

| 8.8  | Control structure for FOC of PMSM                                                                         |

| 8.9  | Circuit diagram of (a) 2-level inverter (b) generalized multilevel inverter.183                           |

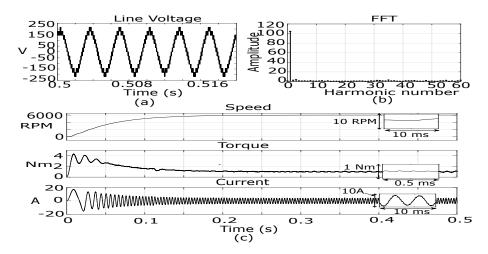

| 8.10 | Simulation result of 2-level inverter with PMSM drive: (a) line to line                                   |

|      | voltage (b) harmonic spectrum (c) speed, torque and current of drive                                      |

|      | at nominal value                                                                                          |

| 8.11 | Simulation result of 5-level inverter with PMSM drive: (a) line to line                                   |

|      | voltage (b) harmonic spectrum (c) speed, torque and current of drive                                      |

|      | at nominal value                                                                                          |

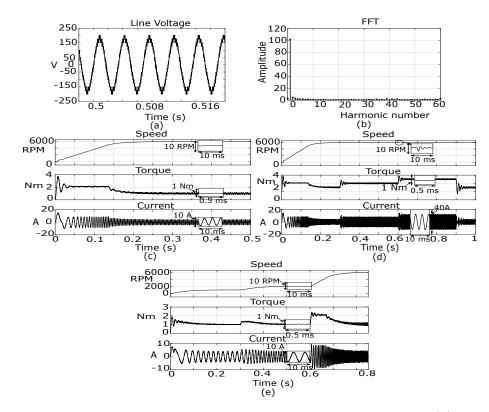

| 8.12 | Simulation result of 7-level inverter with PMSM drive: (a) line to line                                   |

|      | voltage (b) harmonic spectrum (c) speed, torque and current of drive                                      |

|      | at nominal value.                                                                                         |

| 8.13 | Simulation result of 9-level inverter with PMSM drive: (a) Line to                                        |

|      | line voltage (b) harmonic spectrum (c) speed, torque and current of                                       |

|      | drive at nominal value (d) speed, torque and current of drive with                                        |

|      | varying torque (e) speed, torque and current of drive with varying                                        |

|      | speed                                                                                                     |

| 8.14 | (a) $\%$ SOC of battery modules for different inverter levels, analysis    |       |

|------|----------------------------------------------------------------------------|-------|

|      | of (b) % THD (c) torque ripple (d) switching loss for each inverter        |       |

|      | level at modulation indices 1, 0.8, 0.4, 0.2 (e) cost analysis of switches |       |

|      | for each inverter level.                                                   | . 189 |

# **List of Tables**

| 3.1        | Voltage levels and the corresponding conduction states in the 5-level NPC                  |

|------------|--------------------------------------------------------------------------------------------|

| 3.2        | Voltage levels and the corresponding conduction states in a 5-level FC multilevel inverter |

| 3.3        | Output voltage redundancies in a 5-level cascaded inverter [6] 30                          |

| 5.1        | Switching angles in radians and corresponding $THD$ obtained graph-                        |

| 5.2        | ically solving (5.18)                                                                      |

| 5.2        | Harmonic amplitudes in percentage, obtained in load condition 88                           |

| 5.4        | Computed THD% obtained by different modulation techniques 94 $$                            |

| 5.5        | Matrices $Aj \ j = 1, 2$ 98                                                                |

| 5.6        | Vector $b$                                                                                 |

| 5.7        | Computed parameter $C$ and $THD\%$                                                         |

| 5.8        | Grid codes EN 50160 and CIGRE WG 36-05                                                     |

| 5.9        | Comparison between PAWM and technique in [250]                                             |

| 5.10       | Output voltage THD% vs. designed DC link voltages disturbance. $% 123$                     |

| 6.1        | Characteristics of the CYCLONE V FPGA 5CEFA7F31 146                                        |

| 6.2        | Characteristics of ALTERA MAX 10 10M16DAF484                                               |

| 7.1        | H-bridge module nominal operating conditions                                               |

| 8.1        | Comparison of component number requirement per phase voltage                               |

| 0.0        | level among MVSI topologies [362]                                                          |

| 8.2<br>8.3 | Pole voltage redundancies for 5-level inverter                                             |

| 0.0        | PMSM parameters                                                                            |

## 1 Abstract

During the last two decades, the need of reducing global warming, all forms of pollution and the need of increasing energy efficiency in all fields, is transforming the way the energy in produced, transmitted, distributed and utilized. In this scenario, power electronic converters represent a key element because of their "unique" capability to manipulate and/or transform, and/or control huge amounts of electric energy, according to simple or complex control laws implemented using digital computer device. Renewable energy, smart grids, electric transportation cannot be used without power converters, therefore, modern power converters are those unique devices driving the transition from conventional to clean energy.

The existing limits of semiconductor's technology conflict with the high values of power, voltages and currents required in a large amount of applications and for this reason multilevel converters have been proposed because their allow to overcome technological limits of power devices.

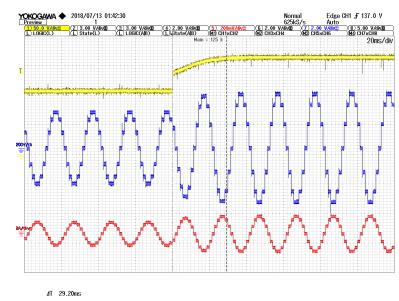

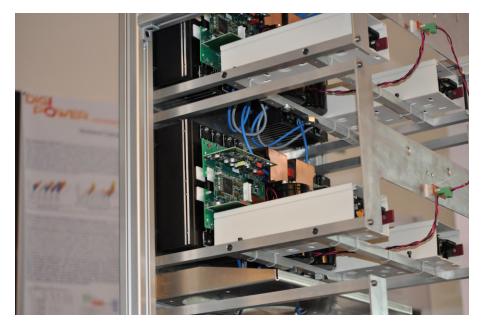

The whole Ph.D. activity, summarized in part with this thesis, has been developed in this context and mostly within the frame of the industrial research project titled: "CoMoDes", by DigiPower Ltd. L'Aquila, a "PMI Innovativa", born in 2007 as University of L'Aquila spin-off [1]. The grant, awarded by the Italian Ministry of Economic Development (MISE) with the number: F/050220/01-02-03/X32 - PON - H2020, Call 2016, has regarded the study and the development of modular multilevel converters (MMC) for the integration of renewable energy sources and for the electric mobility in the smart grid environment. The project, while using a methodology typical of applied scientific research, has addressed almost all main aspects of multilevel converters technology: topologies, applications, control, modulation, hardware and has involved the Author of this Ph.D. Thesis in a significant number of activities.

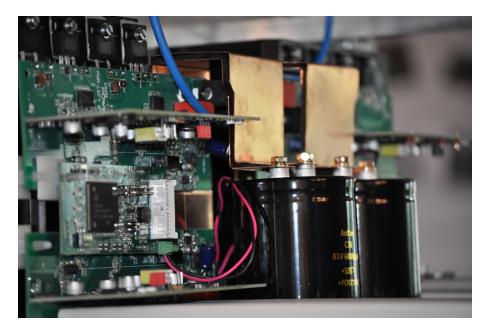

The project has dealt with the study, design and realization of a three-phase, 33level converter with rated phase voltage:  $10 \text{ kV} @ 35 \text{ A}_{\text{rms}}$ , resulting total power close to 1 MW. Some prototypes of the modular multilevel converter are now available at DigiPower Ltd Lab and utilized as R&D systems in relevant research branches, currently: smart grids and electric transportation.

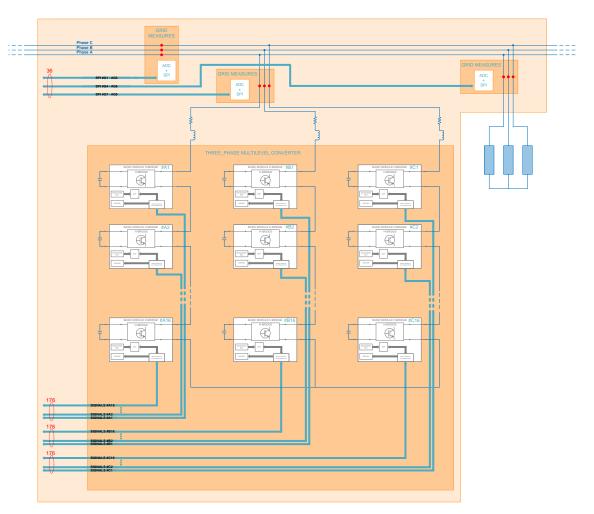

The developed architecture is a cascade H-bridge (CHB) topology and it grants higher flexibility, modularity and fault tolerant characteristics with respect to other CHB-MC. Each H-bridge module is equipped with its own DSP unit, which collects module's information (current, voltage, error status, temperature etc.) and transmits them to the main control board, the latter equipped with a FPGA, a CPLD and a DSP controllers. The main control board analyzes the state of each H-bridge and applies the required modulation signals to the system according to implemented control and modulation algorithms; it takes immediate decisions in case of incoming fault, thus improving the overall reliability and flexibility of the system. The local DSPs can be optionally programmed in order to implement distributed control algorithms, exploiting the unique true multiprocessing capability.

The advanced hardware (HW), combined with innovative fundamental frequency modulations developed in parallel with the HW and with control algorithms, offer high flexibility and efficiency, especially in high power applications; moreover they reduce switching losses and harmonic contents in output waveforms. Therefore, developed system significantly improves the power quality and grants a reduction in the average device switching frequency, while minimizing cost and size of the output power filter.

Author's main contributions to the above project can be found in the following parts:

- Hardware design of the power modules

- Hardware design of the system control board

- Implementation of the innovative modulation techniques for the harmonic content reduction

- Debug, tuning, and implementation of the control algorithms

- Prototype validation and experimental tests.

The design of such a kind of converters is an uncharted problem area and the completion of the whole project including the realization of a fully working experimental prototype and its SW companions has been a true challenge which has required almost three years of work and relevant skills in different areas of the power electronics; the realization of a high power prototype of this kind, requires a huge investment and relevant laboratory facilities: for the above mentioned reasons, the results achieved in this dissertation would not have been possible without the full support of DigiPower Ltd [1] and its very highly qualified staff.

The enhanced performance of the proposed HW is supported by results achieved with the advanced and innovative fundamental frequency modulation techniques, specifically developed and implemented as a part of this PhD thesis.

Operations and functionalities of the converter and of the presented algorithms have been extensively verified by simulation in MATLAB/Simulink framework [2] and then implemented and tested on the prototype. Several tests have been performed choosing different topologies and applications, in particular on a grid-connected three-phase static synchronous compensator (STATCOM) and a three-phase permanent magnet synchronous motor drive.

This work is a step towards studying the proposed topology and it provides a baseline for future analyses of the architecture and its possible improvements.

# 2 Introduction

### 2.1 Background

The smart grid (SG) is the new generation intelligent electricity network which optimizes the energy efficiency through exchanges real-time information between electric suppliers and customers. Two keys technologies fundamental in smart grids are the wide use of distributed renewable energy generators and the power conversion systems, needed by first one in order to rapidly and effectively adapt the values of voltage, current, power, and energy according to the requests.

Moreover, the wide use of such distributed systems requires the application of energy flow balancing techniques for end-user customers with high quality, stability and reliability. In this case, power electronic converters represent the power interfaces and such interconnection causes the electric grid to become the "load side" of the converter. The main role of the power converters in SG is even more evident if the fluctuating nature of the Renewable Energy Systems (RES) is considered, making it necessary the utilization of the energy storage units.

Majority part of renewable energy sources produce direct current (DC) electricity in the output, such as photovoltaic panels (PV) and Fuel Cells (FC). To use the produced DC energy in various kind of loads (AC and/or DC), the DC/DC and/or DC/AC converters should be utilized to adopt the unregulated DC voltage to the regulated and usable one. On the other hand, to connect this kind of renewable energies to the utility grid, DC/AC converters must be used.

In order to connect RES to electric grid, a high power (> 100 kW); and high voltage converter is preferred because of their higher efficiency and because their use become economically convenient only above a certain amount of power.

Multilevel converters (MC) are converters that use more than two voltage levels in order to produce a staircase AC output waveform. They are suitable for applications which require high output voltage, low output harmonic distortion, high efficiency, and high volt-ampere ratings. Moreover, the diversity of voltage levels of renewable energy sources in distributed system makes multilevel inverters an interesting and innovative choice as the proper solution for interconnection of distributed energy sources and for the improvement of power quality and reliability. Thus, the MC topology is being exploited to replace the two-level VSI [3]. The salient features of this topology include:

1. Modularity and scalability, to fulfill high-voltage level requirements.

- 2. Feasibility of the direct connection to high-voltage networks without using transformers and therefore a reducing system size, cost, losses and footprint.

- 3. Superior harmonics performance, due to the high-level of the output voltage waveform, in which a large number of submodules with low rating switches are used, thereby allowing a significant reduction in the filtering requirement.

- 4. A huge number of degrees of freedom in terms of switching patterns and DC supply levels which allow the implementation of advanced modulation technique to increase the performances of the converter.

- 5. Low expense for fault tolerant operation due to utilization of standard, low voltage components, such as 600V-1200V IGBT even in high voltage applications.

There are four main multilevel topologies, which are deeply described in chapter 3: flying capacitor converter (FCC), neutral point clamped (NPC) converter, cascaded H-bridge converter (CHB), and the modular multilevel converter (MMC):

- The flying capacitor converter, uses capacitors to subdivide the output voltage of the converter, which allows multiple voltage levels to be produced.

- The NPC converter, utilizes diodes to produce a multilevel output voltage. To create additional voltage levels, the dc bus capacitor would consist of a string of capacitors with clamping diodes connected at regular intervals.

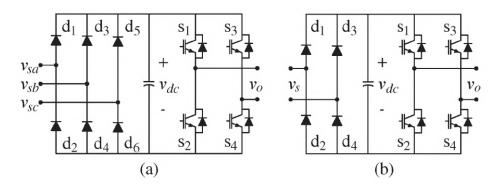

- The cascaded H-bridge converter is the multilevel topology that has, thus far, garnered the most interest for applications to renewable resources and electric drives. It is composed by a number of elemental H-bridge inverters  $N_{inv}$ , connected in series, that generates a number of voltage levels of the phase voltage  $L_{ph}$  equal to  $L_{ph} = 2N_{inv} + 1$ .

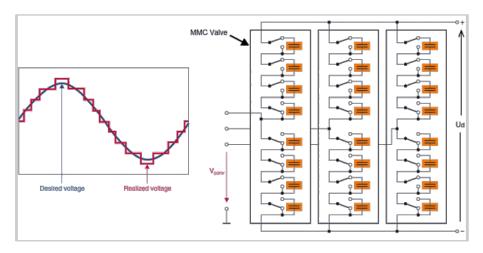

- The MMC was originally developed for medium and high voltage dc transmission and distribution applications. The MMC, consists of three phase legs, each with an upper and lower phase arm. A phase arm is composed of a series of submodules and a small inductor. The inductors are used to limit the rate of change of current during switching transitions in the phase arms and to provide filtering of both ac and dc output currents. The composition of the submodules may vary, but the most common submodule consists of a half-bridge converter.

Several renewable energy sources (batteries, fuel cells, solar cells, wind turbines or micro turbines) can be easily connected through a multilevel inverter to feed a load (off-grid) or interconnect to the ac grid (grid-connected) without voltage balancing problems. Moreover, multilevel inverters can have a lower switching frequency than standard Pulse Width Modulation (PWM) inverters and thus have reduced switching losses. Since the output waveforms of multilevel inverters are in a stepped form, resulting in reduced harmonics compared to a square-wave inverter, hence the the output filter size is reduced and the efficiency is high. Also, the voltage stress on the power electronic switches such as power MOSFETs and/or IGBTs are less in such converters which makes it suitable in medium/high voltage applications.

Furthermore, the interest for multilevel converters in the recent year is exponentially growing also in high power motor drives, electric cars charging stations and in utility for high power applications such as Static Synchronous Compensator (STATCOM) to compensate the grid reactive power.

Multilevel converter topologies are also found suitable for PV applications since, due to the modular structure of PV arrays, different DC voltage levels can easily be provided. Such power converters should have a high reliability, high efficiency, good harmonic performance, low cost, and a small footprint.

Even if the advantages of the multilevel technology are obvious in high power fields, their presence on the market is still lacking. However, in recent years, especially because of the leap forward on the automotive business, also the world leaders in the power electronic field are moving their first steps towards the multilevel technologies.

### 2.2 Outline of Thesis

This dissertation is divided into nine chapters and is structured in four sections:

- **Part 1:** the first section presents an overview of the literature knowledge regards the multilevel converters. It particular:

- chapter 3 presents the state of art of the multilevel converters topologies.

- chapter 4 addresses the state of art of the multilevel modulation techniques.

- Part 2: In chapter 5 are presented some innovative modulation techniques which have been developed during my PhD studies. Also several experimental results and comparisons have been performed and are shown in this chapter.

- **Part 3:** The third part deals with the hardware design of an FPGA-CPLD-DSP based control board used to control the multilevel converter prototypes. All the functionalities of the control board have been described and analyzed.

- **Part 4:** The last section of this thesis presents the initial results obtained in two different applications fields:

- A D-STATCOM application for the power grid stabilization.

- A high power asynchronous motor drive application.

- **Part 5:** Finally, conclusions and the suggestions for future work are included in chapter 9.

## 2.3 Related Publications

All the publications and the activities related to the presented work are listed below:

- C. Buccella, M. G. Cimoroni, M. Tinari and C. Cecati, "A New Pulse Active Width Modulation for Multilevel Converters," in IEEE Transactions on Power Electronics, vol. 34, no. 8, pp. 7221-7229, Aug. 2019.

- C. Buccella, M. G. Cimoroni, V. Patel, M. Tinari and C. Cecati, "Investigation about SHM-PAM procedure for grid connected CHB seven level inverters," 2019 International Conference on Clean Electrical Power (ICCEP), Otranto, Italy, 2019, pp. 413-418..

- V. Patel, M. Tinari, C. Buccella and C. Cecati, "Analysis on Multilevel Inverter Powertrains for E-transportation," 2019 IEEE 13th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Sonderborg, Denmark, 2019, pp. 1-6.

- 4. A.M. Saif, C. Buccella, V. Patel, M. Tinari and C. Cecati, "Design and Cost Analysis for STATCOM in Low and Medium Voltage Systems," IECON 2018

- 44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, 2018, pp. 3938-3943.

- C. Buccella, M. G. Cimoroni, V. Patel, A.M. Saif, M. Tinari, C. Cecati, E. Babaei, "Harmonic elimination procedure for cascaded multilevel inverters having a particular even number of dc sources," IECON 2018 44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, 2018, pp. 1249-1254.

- A. Raciti, A. Rizzo, N. Salerno, G. Susinni, C. Buccella, C. Cecati, M. Tinari "State of the art and emerging solid-state power devices in the perspective of more electric aircraft," 2018 AEIT International Annual Conference, Bari, 2018, pp. 1-6.

- C. Buccella, M. G. Cimoroni, M. Tinari, C. Cecati, S. A. Rizzo, G. Susinnii, A. Raciti, "Single-Phase Chebyshev Algorithm for Harmonics Mitigation in CHB Five-Level Inverters," 2018 AEIT International Annual Conference, Bari, 2018, pp. 1-5.

- V. Patel, C. Buccella, A. M. Saif, M. Tinari and C. Cecati, "Performance Comparison of Multilevel Inverters for E-transportation," 2018 International Conference of Electrical and Electronic Technologies for Automotive, Milan, 2018, pp. 1-6.

- M. G. Cimoroni, M. Tinari, C. Buccella and C. Cecati, "A high efficiency Selective Harmonic Elimination technique for multilevel converters," 2018 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), Amalfi, 2018, pp. 673-677.

C. Buccella, M. G. Cimoroni, H. Latafat, M. Tinari and C. Cecati, "Mixed harmonic elimination and reduction technique for single phase nine level converters," 2017 IEEE 26th International Symposium on Industrial Electronics (ISIE), Edinburgh, 2017, pp. 756-761.

# 3 State of Art: Multilevel Converter (MLC) Structures

#### 3.1 Overview

With the diffusion of renewable energy systems, high power quality of power converters is fundamental for their successful integration within the grid. Therefore, the achievement of strict specifications imposed on harmonics content in order to fulfill grid code limits became one of the most demanding design issue, which can be accomplished only by suitable synthesis of modulation signals [4]. Multilevel Inverters (MLI) operating at frequency close to fundamental are nowadays considered leading topology for achieving such results, due to their capability to produce voltage waveforms with relatively low harmonic content even with reduced output passive filters. In particular, they appear very attractive in high power applications, in which low switching frequency operations are necessary to ensure that intrinsic losses in electronic devices do not affect converter operations and efficiency. Multilevel Converters (MLC) receive wide acceptance in industry and energy systems because they enable the design of medium and high voltage systems with excellent output voltage quality. Compared to the two-level voltage source converter, the simple realization of redundancy, low filter expense, and the reduction of power semiconductor losses and common mode voltages are important additional benefits [5].

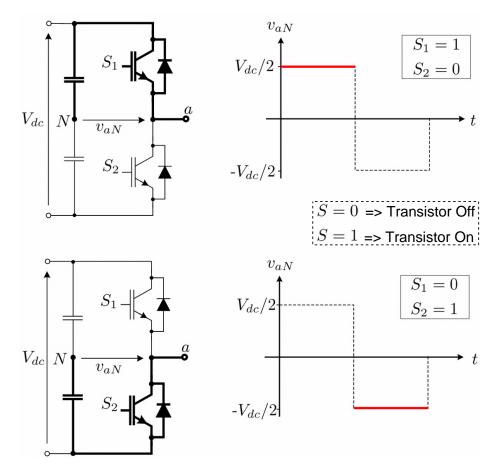

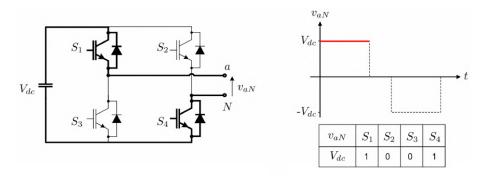

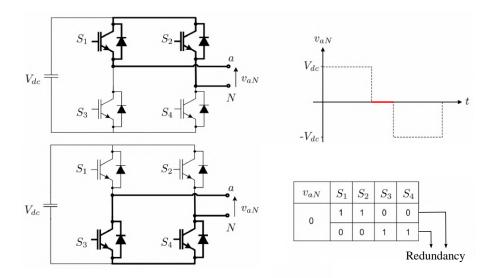

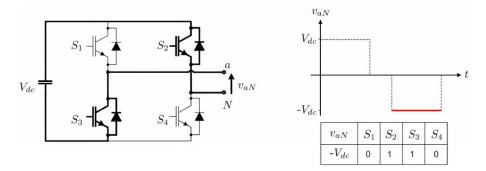

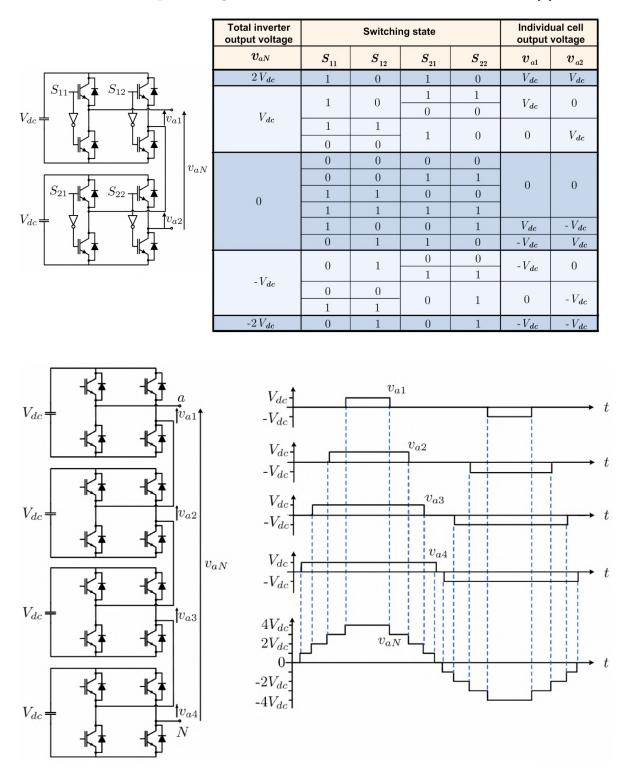

The number of levels of an inverter, is the number of steps in the voltage of the output terminal with respect to any arbitrary internal reference point. One phase leg of a two-level inverter is shown in Fig. 3.1. The conduction states of the power switches (IGBT) determine the output voltage  $(v_{aN})$  status. To avoid any short circuit in the phase leg, the switches must not be On simultaneously.

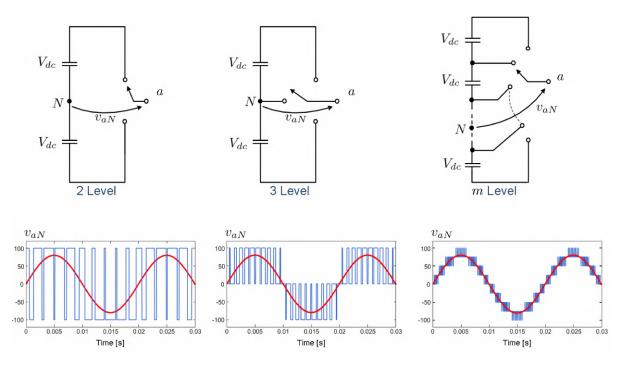

Multilevel inverters include an array of power semiconductors and capacitor voltage sources, the output of which generate voltages with stepped waveforms. The commutation of the switches permits the addition of the capacitor voltages, which reach high voltage at the output, while the power semiconductors must withstand only reduced voltages. Fig. 3.2 shows a schematic diagram of one phase leg of inverters with different numbers of levels, for which the action of the power semiconductors is represented by an ideal switch with several positions. As shown in this figure, a two-level inverter generates an output voltage with two values (levels) with respect

Figure 3.1: One phase leg of a two-level inverter and its output voltage [6].

to the negative terminal N, while the three-level inverter generates three voltages, and so on.

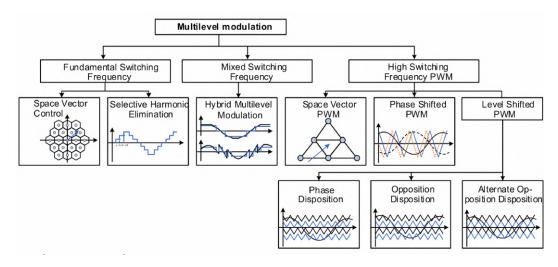

The first multilevel (three-level) inverter introduced by Nabae *et al.* [7] in 1981. By increasing the number of levels in the inverter, more steps can be achieved in the output voltages generating a staircase waveform, which results a reduced harmonic distortion. However, a high number of levels increases the control complexity and introduces capacitor voltage unbalance problems. Four successful different topologies have been proposed for multilevel inverters: diode-clamped (neutral point clamped) [7]; capacitor-clamped (flying capacitors) [8, 9, 10]; cascaded multicell (cascaded H-bridge) with separate dc sources [8, 11, 12]; and Modular Multilevel Converters (MMC) [13]-[16]. In addition, several modulation and control strategies have been developed or adopted for multilevel inverters including the following: multilevel sinusoidal pulse width modulation (PWM), multilevel selective harmonic elimination, and space-vector modulation (SVM). The most attractive features of multilevel inverters are as follows.

1. They can generate output voltages with extremely low distortion and lower  $d_v/d_t$ .

Figure 3.2: Schematic diagram of one phase leg of MLI for two, three and m levels [6].

- 2. They draw input current with very low distortion.

- 3. They generate smaller common-mode (CM) voltage, thus reducing the stress in the motor bearings. In addition, using sophisticated modulation methods, CM voltages can be eliminated [12].

- 4. They can operate with a lower switching frequency.

Currently, three-level neutral point clamped (NPC) or flying capacitor (FC) converters seem preferred due to their cost, but Cascaded H-Bridges (CHB) are gaining interest and applications, due to their superior characteristics and simple modular structure. Therefore, as discussed in [17, 18], many researchers are addressing their attention to this topology. Both traditional NPC and FC multilevel inverters have a practical limit on the number of levels, because the number of respectively required clamping diodes and capacitors in both topologies becomes excessive when the number of levels is high [19].

Among multilevel inverter topologies, cascaded multilevel inverter reaches the higher output voltage and power levels (13.8 kV, 30 MVA) and the higher reliability due to its modular topology. Cascaded multilevel inverters are based on a series connection of several single-phase inverters. This structure is capable of reaching medium output voltage levels using only standard low-voltage mature technology components. Typically, it is necessary to connect three to ten inverters in series to reach the required output voltage. These converters also feature a high modularity degree because each inverter can be seen as a module with similar circuit topology,

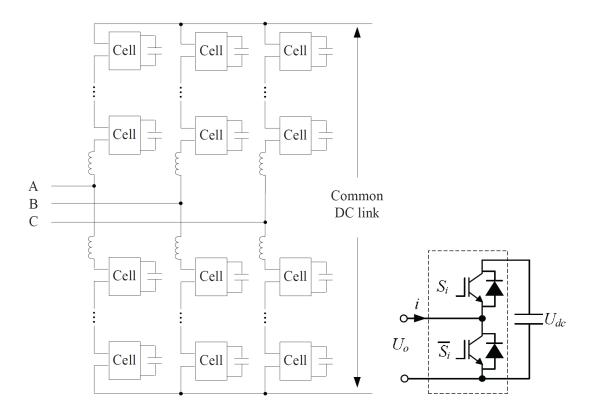

control structure, and modulation [17]. The MMC is an advanced type of series cascaded converters in which half-bridge DC/DC modules with floating capacitor are used as a core module. This converter has a common DC link which makes this topology more useful in HVDC application. But capacitors voltage unbalance problem was also reported in literature for the MMC [20]-[24], [46, 47].

The CHB converter utilizes H-bridge AC/DC modules with separate dc links (capacitors), so its control and modulation is more simpler. The output voltage characteristics of CHB are intrinsically better in two level converters, but further enhancements can be achieved using specific modulation algorithms based on analytical, numerical or optimization methods and capable of harmonic elimination or mitigation [162, 177, 178, 195].

The application of the NPC inverter and its extension to multilevel converter was found in [25]. Although the cascade inverter was invented earlier, its applications did not prevail until the mid–1990s. Two major patents [26, 27] were filed to indicate the superiority of cascade inverters for motor drive and utility applications. Due to the great demand of medium-voltage high-power inverters, the cascade inverter has drawn tremendous interest ever since. Several patents were found for the use of cascade inverters in regenerative-type motor drive applications [28]–[30]. The last entry for U.S. multilevel inverter patents, which were defined as the capacitorclamped multilevel inverters, came in the 1990s [31, 32]. Today, multilevel inverters are extensively used in high-power applications with medium voltage levels. The field applications include use in laminators, mills, conveyors, pumps, fans, blowers, compressors, and so on.

In this chapter sec. 3.2, sec. 3.3, sec. 3.4 and sec. 3.5 present diode-clamped, capacitorclamped, cascaded H-bridge and MMC multilevel structures, respectively. In ?? some other introduced topologies for multilevel converters are presented in brief. Finally, sec. 3.6 presents the summary of this chapter.

## 3.2 Diode-Clamped (Neutral Point Clamped) MLC

The diode-clamped inverter was also called the neutral-point clamped (NPC) inverter when it was first used in a three-level inverter in which the mid-voltage level was defined as the neutral point. Because the NPC inverter effectively doubles the device voltage level without requiring precise voltage matching, the circuit topology prevailed in the 1980s.

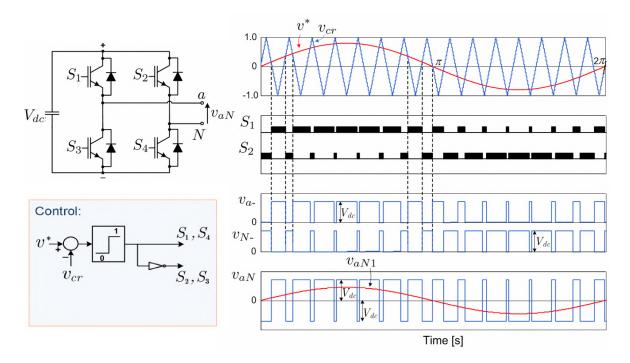

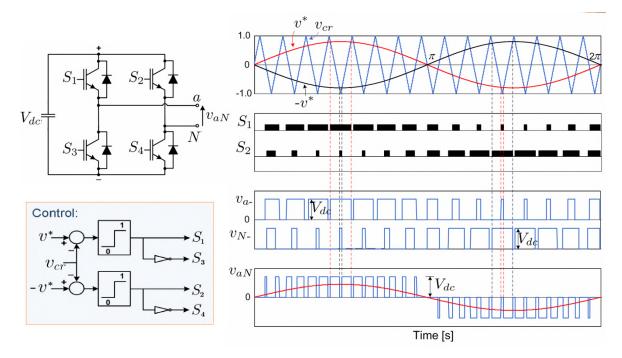

#### 3.2.1 The Main Structure and Conduction States

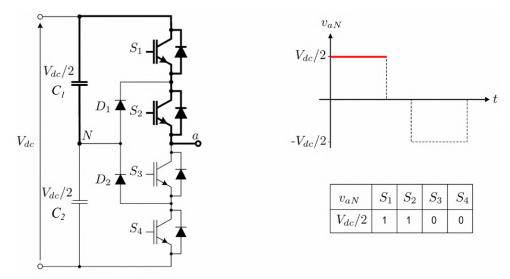

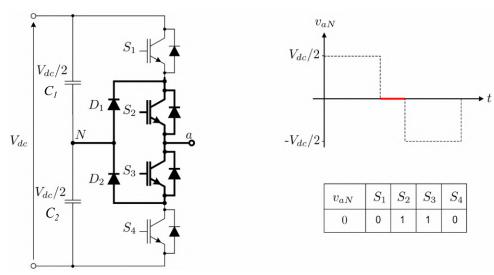

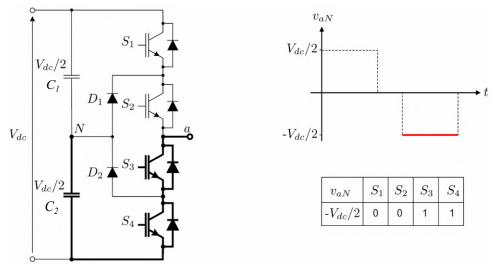

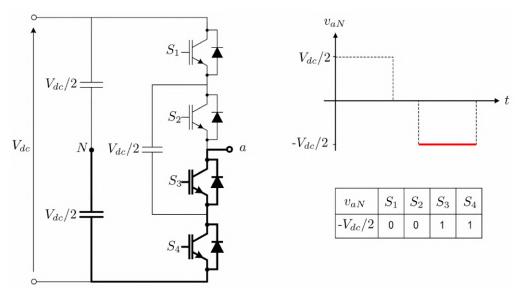

A *m*-level diode-clamped inverter has m - 1 capacitors in dc bus and produces m levels in output voltage. A three-level NPC is shown in Fig. 3.3. In this circuit,

the dc-bus voltage is split into three levels by two series-connected bulk capacitors,  $C_1$  and  $C_2$ . The middle point of the two capacitors N can be defined as the neutral point. The output voltage  $v_{aN}$  has three states:  $V_{dc}/2$ , 0, and  $-V_{dc}/2$ . For voltage level  $V_{dc}/2$ , switches  $S_1$  and  $S_2$  need to be turned on; for  $-V_{dc}/2$ , switches  $S_3$  and  $S_4$  need to be turned on; and for the 0 level,  $S_2$  and  $S_3$  need to be turned on, as shown in Fig. 3.3a, Fig. 3.3c and Fig. 3.3b, respectively.

The key components that distinguish this circuit from a conventional two-level inverter are  $D_1$  and  $D_2$ . These two diodes clamp the switch voltage to half the level of the dc-bus voltage. When both  $S_1$  and  $S_2$  turn on, the voltage across  $S_3$  and  $S_4$  (across *a* and the emitter of  $S_4$ ) is  $V_{dc}$ . In this case, balances out the voltage sharing between  $S_3$  and  $S_4$  with  $S_3$  blocking the voltage across  $C_1$  and  $S_4$  blocking the voltage across  $C_2$ .

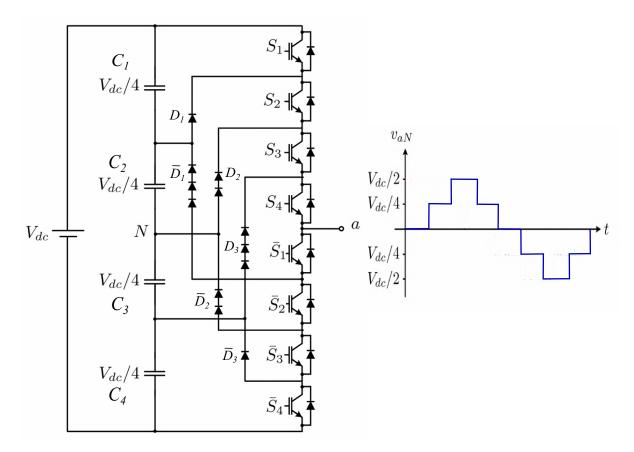

Fig. 3.4 shows a five-level NPC converter in which the dc bus consists of four capacitors,  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ . For dc-bus voltage  $V_{dc}$ , the voltage across each capacitor is  $V_{dc}/4$ , and each device voltage stress will be limited to one capacitor voltage level  $V_{dc}/2$  through clamping diodes.

To explain how the staircase voltage is synthesized, the neutral point N is considered as the output phase voltage reference point. There are five switch combinations to synthesize five level voltages across a and N.

- 1. For voltage level  $v_{aN} = V_{dc}/2$ , turn on all upper switches  $S_1 S_4$ .

- 2. For voltage level  $v_{aN} = V_{dc}/4$ , turn on three upper switches  $S_2-S_4$  and one lower switch  $\bar{S}_1$ .

- 3. For voltage level  $v_{aN} = 0$ , turn on two upper switches  $S_3$  and  $S_4$  and two lower switches  $\bar{S}_1$  and  $\bar{S}_2$ .

- 4. For voltage level  $v_{aN} = -V_{dc}/4$ , turn on one upper switch  $S_4$  and three lower switches  $\bar{S}_1 \bar{S}_3$ .

- 5. For voltage level  $v_{aN} = -V_{dc}/4$ , turn on all lower switches  $\bar{S}_1 \bar{S}_4$ .

Generated voltage levels and the corresponding conduction states of the switches are given in Tab. 3.1. In this table, the state 1 means the corresponding switch is On, and state 0 means the corresponding switch is Off. It should be noticed that, each switch commutes only one time in each cycle.

Four complementary switch pairs exist in each phase. The complementary switch pair is defined such that turning on one of the switches will exclude the other from being turned on. In this example, the four complementary pairs are  $(S_1, \bar{S}_1), (S_2, \bar{S}_2), (S_3, \bar{S}_3)$ , and  $(S_4, \bar{S}_4)$ .

#### 3.2.2 Characteristics of The NPC multilevel inverters

• To block the clamping diodes, high voltage ratings is needed: Although each active switching device is only required to block a voltage level of

(a) Generating of a positive in output voltage  $v_{aN}$

(b) Generating of a zero in output voltage  $v_{aN}$

(c) Generating of a negative in output voltage  $v_{aN}$

**Figure 3.3:** One phase leg of a three-level NPC with conduction states [6].  $_{20}$

Figure 3.4: One phase leg of a five-level NPC and its output voltage [6].

$V_{dc}/(m-1)$ , in which m is number of the levels of the multilevel inverter, the clamping diodes must have different voltage ratings for reverse voltage blocking. For example, by considering  $\overline{D}_1$  of Fig. 3.4, when lower devices  $\overline{S}_2-\overline{S}_4$  are turned on,  $\overline{D}_1$  needs to block three capacitor voltages, or  $3V_{dc}/4$ . Similarly,  $D_2$  and  $\overline{D}_2$  need to block  $2V_{dc}/4$ , and  $D_3$  needs to block  $3V_{dc}/4$ . Assuming that each blocking diode voltage rating is the same as the active device voltage rating, the number of diodes required for each phase will be  $(m-1) \times (m-2)$ . This number represents a quadratic increase in . When is sufficiently high, the number of diodes required will make the system impractical to implement. If the inverter runs under PWM, the diode reverse recovery of these clamping diodes becomes the major design challenge in high-voltage high-power applications.

• Unequal ratings of active switching devices: As shown from Tab. 3.1,  $S_1$  only conducts in  $v_{aN} = V_{dc}/2$ , whereas  $S_4$  conducts in all of the cycle except in  $v_{aN} = -V_{dc}/2$ . Such unequal conduction cycle needs the switching devices with different current and power ratings. The outer switches may be over sized, while the average conduction of the switching devices are used for inverter designing, and the ratings of the inner switches may be under sized.

| Voltage level $(v_{aN})$ | Switches conduction states |       |       |       |             |             |             |             |

|--------------------------|----------------------------|-------|-------|-------|-------------|-------------|-------------|-------------|

| voltage level $(v_{aN})$ | $S_1$                      | $S_2$ | $S_3$ | $S_4$ | $\bar{S}_1$ | $\bar{S}_2$ | $\bar{S}_3$ | $\bar{S}_4$ |

| $v_{aN} = V_{dc}/2$      | 1                          | 1     | 1     | 1     | 0           | 0           | 0           | 0           |

| $v_{aN} = V_{dc}/4$      | 0                          | 1     | 1     | 1     | 1           | 0           | 0           | 0           |

| $v_{aN} = 0$             | 0                          | 0     | 1     | 1     | 1           | 1           | 0           | 0           |

| $v_{aN} = -V_{dc}/4$     | 0                          | 0     | 0     | 1     | 1           | 1           | 1           | 0           |

| $v_{aN} = -V_{dc}/2$     | 0                          | 0     | 0     | 0     | 1           | 1           | 1           | 1           |

Table 3.1: Voltage levels and the corresponding conduction states in the 5-level NPC.

This unequal condition would be an advantage in conventional transformer coupled multi-pulse converters with 6-pulse operation of each converter.

• Capacitors unbalance problem: In the most applications of power converters, active power transfer from ac side to dc (rectifier operation) and vice versa (inverter operation) is essential. When the NPC converter works with unity power factor, charging time for rectifying operation (inverter mode charging time) is different for each capacitor. This capacitor charging profile occurs in each cycle and results in capacitors voltage unbalance. For the diode-clamped multilevel inverter with a number of levels (m) greater than three (i.e., m > 3), each voltage level can be balanced only when used for var compensation [33]. For motor drives that involve real power transfer, the diode-clamped multilevel inverter require either isolated dc power sources, an additional voltage balancing circuit [34], or a back-to-back system with each voltage level connected back-to-back and voltage balancing control [35, 36]. In [37], dc capacitor voltage equalization control schemes of a five-level diode-clamped multilevel inverter-based DSTATCOM are presented with the dc-dc converter circuit for equalization.

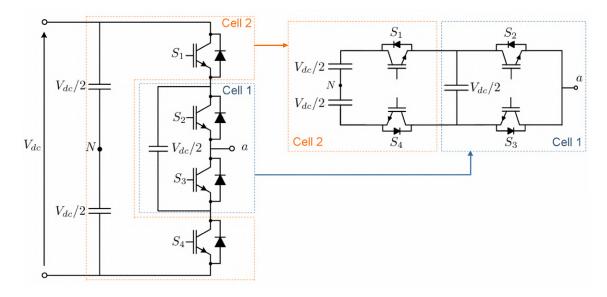

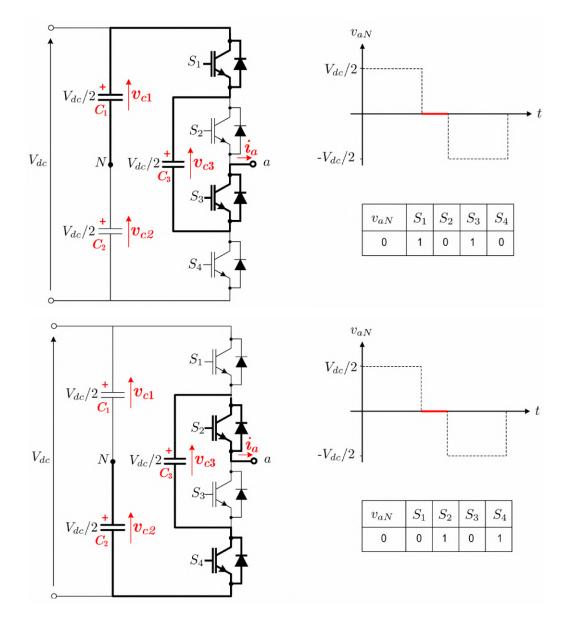

### 3.3 Capacitor-Clamped (Flying Capacitor) MLC

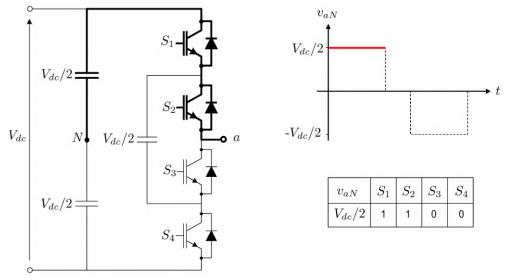

Fig. 3.5 illustrates the fundamental building block of a phase-leg capacitor-clamped inverter. The circuit has been called the flying capacitor (FC) inverter [8, 10] with independent capacitors clamping the device voltage to one capacitor voltage level. As shown in this figure, flying capacitor inverter has a modular topology and also called the multicell converter. Each cell is composed by 2 switches and 1 capacitor. additional cells can be connected in series to increase the number of output levels of the inverter. The switches of each cell are complementary controlled (e.g.:  $S_1 = \bar{S}_4$ ).

The inverter in Fig. 3.5 provides a three-level output across a and N, i.e.,  $v_{aN} = V_{dc}/2$ , 0, or  $v_{aN} = -V_{dc}/2$ . One phase-leg of a three-level FC inverter and conduction states of switches corresponding to each voltage level in the output are shown in

Figure 3.5: The fundamental building block of one phase-leg of a three-level FC inverter [6].

Fig. 3.6 and Fig. 3.7. For voltage level  $V_{dc}/2$ , switches  $S_1$  and  $S_2$  need to be turned on; for  $-V_{dc}/2$ , switches  $S_3$  and  $S_4$  need to be turned on; and for the 0 level, either pair  $(S_1, S_3)$  or  $(S_2, S_4)$  needs to be turned on. There are two possibilities for generating 0-level in the output, this property is called inverter output redundancy. Regarding to Fig. 3.7 and considering  $i_a > 0$ , clamping capacitor  $C_3$  is charged (increase the voltage) and dc-bus capacitor  $C_1$  is discharged (reduce the voltage) when  $S_1$  and  $S_3$  are turned on, and  $C_3$  is discharged and  $C_2$  is charged when  $S_2$ and  $S_4$  are turned on. The opposite charging status are occurred with the same switching condition when  $i_a < 0$ . The charge of  $C_1$ ,  $C_2$  and  $C_3$  can be balanced by proper selection of the 0-level switch combination.

(a) Generating of a positive in output voltage  $v_{aN}$

(b) Generating of a negative in output voltage  $v_{aN}$

Figure 3.6: One phase-leg of a three-level FC inverter and conduction states[6].

Figure 3.7: Generating of a zero level in FC inverter output voltage  $v_{aN}$  and conduction states [6].

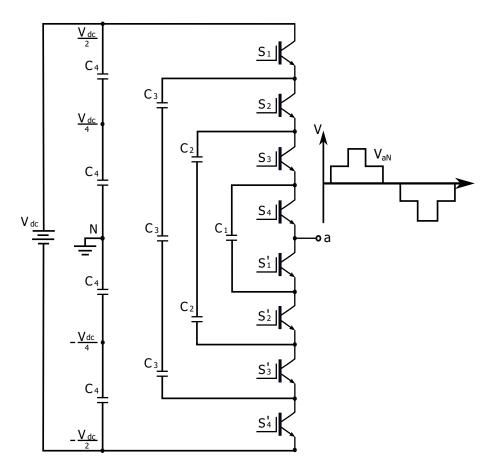

The voltage synthesis in a five-level capacitor-clamped converter has more flexibility than a diode-clamped converter. Using Fig. 3.8 as the example, the voltage of the five-level phase-leg a output with respect to the neutral point N,  $v_{aN}$ , can be synthesized by the following switch combinations.

- 1. For voltage level  $v_{aN} = V_{dc}/2$ , turn on all upper switches  $S_1 S_4$ .

- 2. For voltage level  $v_{aN} = V_{dc}/4$ , there are three combinations:

- a)  $S_1, S_2, S_3, S'_1$  ( $v_{aN} = V_{dc}/2$  of upper  $C_4$ 's  $-V_{dc}/4$  of  $C_1$ );

- b)  $S_2, S_3, S_4, S'_4$  ( $v_{aN} = 3V_{dc}/4$  of  $C_3$ 's  $-V_{dc}/2$  of lower  $C_4$ 's); and

- c)  $S_1, S_3, S_4, S'_3$  ( $v_{aN} = V_{dc}/2$  of upper  $C_4$ 's  $-3V_{dc}/4$  of  $C_3$ 's  $+V_{dc}/2$  of  $C_2$ 's).

- 3. For voltage level  $v_{aN} = 0$ , there are six combinations:

- a)  $S_1, S_2, S'_1, S'_2$  ( $v_{aN} = V_{dc}/2$  of upper  $C_4$ 's  $-V_{dc}/2$  of  $C_2$ 's);

- b)  $S_3, S_4, S'_3, S'_4$  ( $v_{aN} = V_{dc}/2$  of  $C_2$ 's  $-V_{dc}/2$  of lower  $C_4$ );

- c)  $S_1, S_3, S'_1, S'_3$  ( $v_{aN} = V_{dc}/2$  of upper  $C_4$ 's  $-3V_{dc}/4$  of  $C_3$ 's  $+V_{dc}/2$  of  $C_2$ 's  $-V_{dc}/4$  of  $C_1$ );

- d)  $S_1, S_4, S'_2, S'_3$  ( $v_{aN} = V_{dc}/2$  of upper  $C_4$ 's  $-3V_{dc}/4$  of  $C_3$ 's  $+V_{dc}/4$  of  $C_1$ );

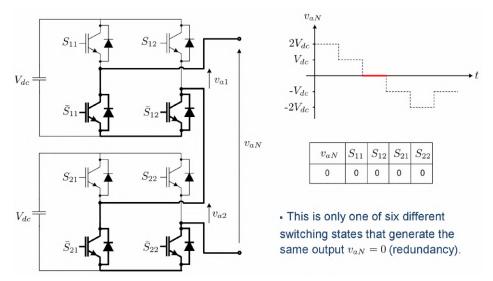

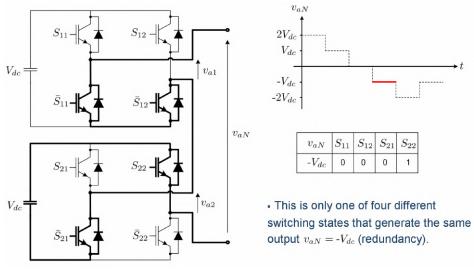

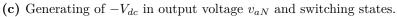

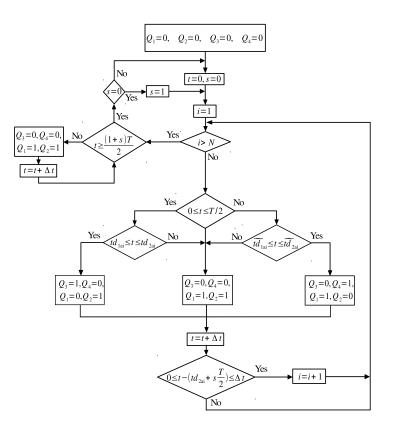

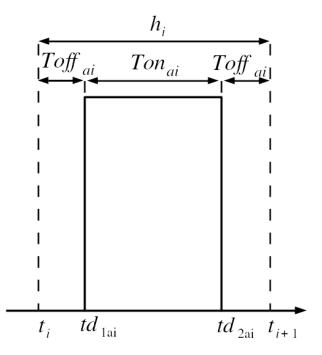

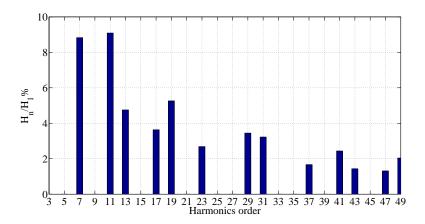

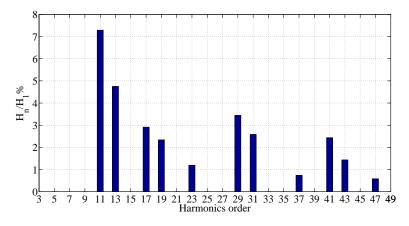

- e)  $S_2$ ,  $S_4$ ,  $S'_2$ ,  $S'_4$  ( $v_{aN} = 3V_{dc}/4$  of  $C_3$ 's  $-V_{dc}/2$  of  $C_2$ 's  $+V_{dc}/4$  of  $C_1 V_{dc}/2$  of lower  $C_4$ 's); and