Received November 28, 2017, accepted December 29, 2017, date of publication January 9, 2018, date of current version March 9, 2018.

Digital Object Identifier 10.1109/ACCESS.2018.2789400

# **MoVES: A Model-Driven Methodology for Vehicular Embedded Systems**

ALESSIO BUCAIONI<sup>[0]</sup>, LORENZO ADDAZI<sup>1</sup>, ANTONIO CICCHETTI<sup>1</sup>, FEDERICO CICCOZZI<sup>[0]</sup>, ROMINA ERAMO<sup>3</sup>, SAAD MUBEEN<sup>101,2</sup>, (Senior Member, IEEE), AND MIKAEL SJÖDIN<sup>1</sup> School of Innovation, Design and Engineering, Mälardalen University, 721 23 Västerås, Sweden

Corresponding author: Alessio Bucaioni (alessio.bucaioni@mdh.se)

This work was supported in part by the Swedish Knowledge Foundation (KKS) through the PreView and MOMENTUM projects and in part by the Swedish Research Council (VR) through the SynthSoft project.

**ABSTRACT** This paper introduces a novel model-driven methodology for the software development of real-time distributed vehicular embedded systems on single- and multi-core platforms. The proposed methodology discloses the opportunity of improving the cost-efficiency of the development process by providing automated support to identify viable design solutions with respect to selected non-functional requirements. To this end, it leverages the interplay of modeling languages for the vehicular domain whose integration is achieved by a suite of model transformations. An instantiation of the methodology is discussed for timing requirements, which are among the most critical ones for vehicular systems. To support the design of temporally correct systems, cooperation between EAST-ADL and the Rubus component model is opportunely built-up by means of model transformations, enabling timing-aware design and model-based timing analysis of the system. The applicability of the methodology is demonstrated as the proof of concepts on industrial use cases performed in cooperation with our industrial partners.

**INDEX TERMS** Model-driven development, vehicular embedded systems, EAST-ADL, component model, model transformations.

#### I. INTRODUCTION

As vehicles transitioned from being mechanical-intensive to software-intensive systems [1], a cost-effective software development became paramount in the vehicular domain. Researchers and practitioners agreed that abstraction and automation, the founding pillars of Model-Driven Engineering (MDE), could be game changers towards the achievement of a cost-effective software development process as they contribute to shorten the development time and employ expensive resources more efficiently [2]. To this end, several domain-specific modelling languages were introduced both for designing the vehicular software and for representing its non functional properties such as timing. Among other languages, the Electronics Architecture and Software Technology Architecture Description Language (EAST-ADL) has been developed by the automotive industry to support modelling of vehicular functions and both their software realisation and desired non functional properties [3]. Within EAST-ADL, the system modelling is performed at four different levels of abstraction which are vehicle-, analysis-, design- and implementation-level (from highest to lowest abstraction level). The requirements on the vehicle functionality of the system are captured at the vehicle level. At the analysis level, the system is defined in terms of abstract functional architecture with a provision for highlevel analyses. Typically, the vehicular software is modelled at the design level by means of function, hardware and allocation models. At the implementation level, the design models are enriched with detailed execution information on e.g., timing (worst-case execution time, etc.). The implementation models are defined by means of other languages, such as the AUTomotive Open System ARchitecture (AUTOSAR) [4] or the Rubus Component Model (RCM) [5]. Often, implementation models are used as the base for code synthesis. However, support to models integration (e.g., among EAST-ADL and RCM models) in the development of vehicular embedded systems is still scarce and the translation from design- to implementation-level is mainly performed manually. Too often, this lack of automation defers the verification of non functional properties to the last phases of the development process. Empirical research shows that modifications during these phases can be 40 times more

<sup>&</sup>lt;sup>2</sup>Arcticus Systems AB, 175 43 Järfälla, Sweden

<sup>&</sup>lt;sup>3</sup>Department of Information Engineering, Computer Science and Mathematics, University of L'Aquila, 67100 L'Aquila, Italy

expensive than the same modifications done during the design of the software and can introduce inconsistencies if they are not properly back propagated [6].

In this context, our hypothesis is that providing automation for model integration would enable early verification of non functional requirements (e.g. timing requirements) during the design of vehicular embedded systems thus improving the cost-efficiency of their development. In fact, early verification of non functional requirements would limit the need for expensive modifications on the almost ready-to-deliver software, and automation would reduce the overall development time as well as enhance the use of expensive (engineering) resources.

In this paper, we propose a solution for early verification of non functional requirements by introducing MoVES, a model-driven methodology for the development of distributed vehicular real-time embedded systems on singleand multi-core platforms. Considering the importance of timing in the development of vehicular real-time systems, as acknowledged by several international projects and industrial initiatives (TIMMO-2-USE<sup>1</sup> and AUTOSAR.<sup>2</sup>), the proposed methodology is instantiated to support the development and architectural exploration of system-designs with temporal awareness. MoVES leverages the interplay of EAST-ADL and RCM for expressing functional and implementation models, respectively. Moreover, it features a fully automated mechanism defined in terms of six different model transformations that describe precise relationships between EAST-ADL and RCM. In particular, starting from the EAST-ADL function and hardware models, model transformations generate a set of RCM models. Model transformations automatically generate allocation information on the RCM models from the EAST-ADL allocation model, too. As there might be multiple implementation models for the same design, a source EAST-ADL model cannot be univocally translated into a single target RCM model [7]. Currently, most approaches only consider one particular model out of the many possible alternatives [8]. In this work, we leverage the properties of a constraint-based transformation language, the Janus Transformation Language [9] (JTL), to automatically derive all the possible RCM models entailing meaningful and unique timing and allocation configurations. Timing analysis is run on the generated RCM models. Eventually, model transformations propagate the generated RCM models and the related timing verification results to the design level for enabling timing-aware design decisions. It is important to note that, the process of generating and analysing RCM models is transparent to the engineer and can be guided by means of logic constraints. Moreover, the engineer does not have to manually define or investigate RCM models, but rather select the preferred RCM models from the set of the automatically generated ones. We validated MoVES through a set proof of concepts conducted

in tight cooperation with our industrial partners in the automotive domain. These showed promising results in terms of i) applicability of the methodology and ii) reduction of late modifications at implementation level. The main scientific contributions brought by MoVES are:

- a mechanism for the automatic translation of design models into implementation models,

- a mechanism for the automatic allocation of software to hardware, and

- a mechanism for the back-propagation of the verification results and related implementation models to design models

The rest of the paper is organised as follows. Section II sets the background for this research work along with its contributions and relations with authors' previous work. Section III describes the methodology and its constituents. Section V describes the application of the methodology on a running example mimicking industrial settings. Section VI discusses strengths and weakness of the proposed methodology. Section VII describes related approaches documented in the literature and compares them to our solution. Finally, Section VIII concludes the paper.

#### II. BACKGROUND

MDE is a discipline which aims at improving software development by employing abstraction and automation by using models, metamodels and model transformations [2]. Metamodels formalise the requirements, the structure and the behaviour of software systems within a particular domain. Models allow to design software systems declaratively using the elements and the concepts formalised by the metamodels, thus using constructs pertaining to the problem domain rather than constructs pertaining to the underlying technology. Model transformations are automatic means for analysing models and for synthesising new artefacts (models, source code, etc.) from a set of source models [10]. In the automotive domain, as vehicle transitioned from being mechanical- to software-intensive systems [11], MDE has gained industrial recognition as demonstrated by several international initiatives and projects, such as EAST-ADL [3], RCM [5] and AUTOSAR [4].

In the followings, we describe the background of this research work and its contribution in terms of the modelling languages and the model-based timing analysis leveraged for the definition of MoVES. In particular, in Section II-A and in Section II-B we introduce and describe the main elements of the EAST-ADL and RCM languages, respectively. In Section II-C we discuss the leveraged timing analysis, while in Section II-D we detail the contributions presented in this paper and put them in relation to the authors' previous work.

## A. EAST-ADL

EAST-ADL is a modelling language which captures the essentials of vehicular Electrical and Electronic (E/E) systems concerning their documentation, design, analysis and synthesis. EAST-ADL is specified through ten different

<sup>&</sup>lt;sup>1</sup>https://itea3.org/project/timmo-2-use.html

<sup>&</sup>lt;sup>2</sup>https://www.autosar.org

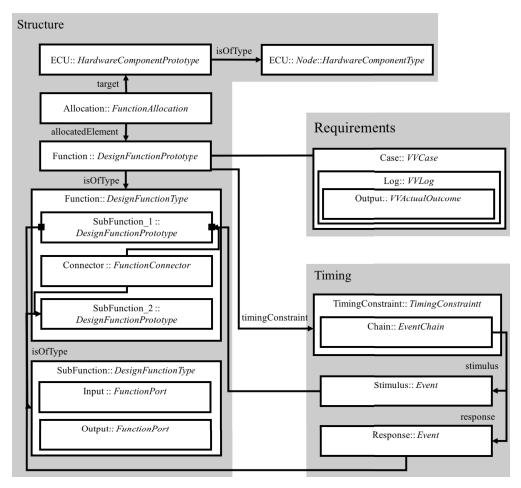

packages, each of which addresses different aspects of vehicular E/E system and their development. In the proposed instantiation of the methodology, we leverage specific concepts from the *structure*, *requirements* and *timing* packages.<sup>3</sup>

The structure package serves for the specification of the software architecture in terms of basic elements and interactions among them. In order to ensure separation of concerns through the development process, the structure package makes use of four abstraction levels, which are *vehicle*, *analysis*, *design* and *implementation*. However, such a separation is only conceptual and some modelling elements can span over several abstraction levels. MoVES connects to the design level and more specifically to the *FunctionalDesignArchitecture*, *HardwareDesignArchitecture* and *Allocation* concepts.

Within EAST-ADL, a FunctionalDesignArchitecture describes how software functions interact. At this level, software functions are represented by means of Design-FunctionPrototype elements linked by FunctionConnector elements. A DesignFunctionPrototype is typed to a DesignFunctionType element which specifies its interface, in terms of FunctionPort elements, and its inner architecture, in terms of additional DesignFuntionPrototype elements. Within EAST-ADL, a HardwareDesignArchitecture describes the physical architecture of the vehicular embedded system. The basic modelling entity is the *HardwareCom*ponentPrototype which is typed to a HardwareComponentType. The HardwarePortConnector elements model the communication between two or more HardwareComponent-Prototype elements by connecting the related *HardwarePort* elements. An EAST-ADL Allocation model consists of a set of FunctionAllocation elements binding AllocatableElement to AllocationTarget elements. AllocatableElement is an abstract superclass which specifies the elements that can be allocated. DesignFunctionPrototype and FunctionConnector are defined as extensions of the AllocatableElement superclass. Similarly, AllocationTarget is an abstract superclass which specifies to which elements an AllocatableElement can be allocated. HardwareComponentPrototype and HardwarePortConnector elements are defined as extensions of the AllocationTarget class. Within the proposed methodology, the concepts from the function, hardware and allocation models are used by the model transformations for the automatic generation of RCM models, as described later.

In this work, we show an instantiation of MoVES focusing on the verification of timing requirements. Therefore, let us see how the timing requirements and properties are modelled within EAST-ADL. The EAST-ADL timing package contains concepts for modelling the timing constraints stemming from the extra-functional requirements. Within EAST-ADL, a timing constraint is modelled by means of *TimingConstraint* elements, which are associated to DesignFunctionPrototype elements. The specification of the timing constraints is realised using two *Event* elements, which mark the scope

of the related timing constraint and are contained within an *EventChain* element. The EventChain and Event elements are used by the proposed methodology for the specification of automatically generated timing constraints in the RCM models.

The requirement package offers means for describing the properties that the vehicular embedded system has to possess and their verification. To this end, the requirement package is further divided into two sub-packages which are Use-Cases and Verification Validation. MoVES leverages specific concepts from the latter only. Within the VerificationValidation package, the VVCase elements represent concrete test activities which are associated to the Design Fucntion-Prototype elements. A VVCase is modelled in terms of the VVProcedure and an VVLog elements which represent the adopted verification and validation technique and its description, respectively. A VVLog element is modelled in terms of a VVActualOutcome element, which specifies the actual output of the verification and validation activity. The proposed methodology uses the VVLog elements for back propagating the RCM models together with their timing verification results to the related EAST-ADL model. Figure 1 shows a simplified EAST-ADL model represented as a block diagram using the EAST-ADL concepts discussed above. The model depicts a DesignFunctionPrototype called Function, which is allocated to a HardwareComponentPrototype called ECU. The Function and ECU elements are typed to the related DesignFunctionType and HardwareComponent-Type, respectively. Accordingly, ECU is an atomic node while Function is composed by two sub-functions called SubFunction\_1 and SubFunction\_2 connected via a FunctionConnector called *Connector*. Additionally, Function is associated with a VVCase called Case and a timing constraint called TimingConstraint.

#### B. RCM

RCM is a modelling language for the predictable development of resource-constrained embedded real-time systems developed by Arcticus Systems<sup>4</sup> in collaboration with Mälardalen University. With respect to the EAST-ADL structural abstraction levels, RCM acts at the implementation level and it is currently used by several OEM, Tier-1 and Tier-2 companies (e.g., Volvo Construction Equipment, BAE Systems Hägglunds, Hoerbiger and Knorr Bremse) in the vehicular domain. In its current definition, RCM provides support for the modelling of the software architecture, the execution platform, the allocation information and the timing properties of vehicular embedded systems<sup>5</sup> [12]. Within RCM, the embedded software architecture is modelled by means of the Software Function (SWC) elements and interactions among them. An SWC is the lowest-hierarchical element, which encapsulates basic software functions, and is defined

<sup>&</sup>lt;sup>3</sup>Please note that the complete explanation of EAST-ADL is outside the scope of this work. The interested reader can refer to [3].

<sup>&</sup>lt;sup>4</sup>https://www.arcticus-systems.com

<sup>&</sup>lt;sup>5</sup>Please note that the complete explanation of the RCM language is outside the scope of this work. The interested reader can refer to [12].

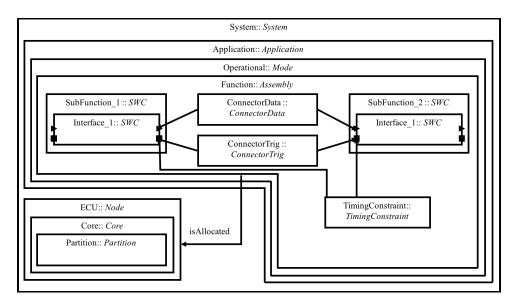

FIGURE 1. Simplified EAST-ADL model containing concepts from the EAST-ADL structure, timing and requirements packages.

by a Behaviour and an Interface elements. The Interface element is responsible for grouping the ports of a SWC. As RCM distinguishes between data and control flows among SWCs, an interface element contains two kinds of port: data and control. The interactions among SWCs are modelled by means of Connector elements. SWCs can be grouped in Assembly elements for constructing the software architecture in a hierarchical manner. SWCs and Assembly elements are contained in Mode elements, which are means for distinguishing different states or conditions in a system. For example, a system can execute the start-up mode when bootstrapping and afterwards shifts to the operational mode. Mode elements are contained within Application elements, which represent independent software functionalities of the system. Application elements provide means for isolating different software functionalities as well as for specifying the safetycriticality level in accordance to the ISO 26262 standard for the functional safety of road vehicles [13]. We refer to the RCM software models as the RCM models which contain the modelling elements for representing the software architecture, only. As the main goal of RCM is to provide support for the development of predictable vehicular embedded systems, timing properties and constraints are pivotal in the language, and they can be specified at different hierarchical levels of the software architecture (Application, Mode, Assembly). Timing constraints are modelled by Timing Constraint elements which are specified on the data ports of the related software element. Within RCM, the execution platform of the vehicular embedded system under development is modelled in terms of Node, Core and Partition elements. A Node element models the specific processor architecture and defines a unique run-time environment for the software architecture. A Node element contains one or more Core elements, which model the processing or computing unit of a Node element. Similarly, Core elements can contain one or more Partition elements, which represent the logical division of a Core elements into multiple computing resources. We refer to the RCM execution platform models as the RCM models which contain the modelling elements for representing the execution platform, only. Allocation information is modelled by means of the isAllocated relation specified between any two Allocatable and Allocator elements. Allocatable is an abstract superclass which specifies the RCM software elements that can be allocated. Application, Mode, Assembly and SWC

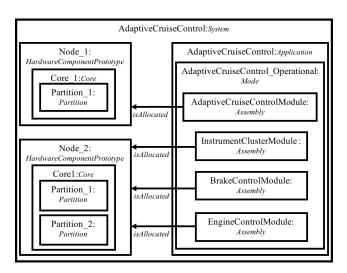

FIGURE 2. Simplified RCM model.

elements are defined as extensions of the Allocatable superclass. Similarly, Allocator is an abstract superclass which specifies to which execution platform element an Allocatable element can be allocated. Node, Core and Partition elements are defined as extensions of the AllocationTarget class.

Figure 2 shows a simplified RCM model represented as a block diagram using the RCM concepts described above. In particular, the model depicts a System called *System* which consists of a Node called *ECU* and an Application called *Application*. ECU is modelled as a single-core and single-partition node. Application is modelled by means of a Mode called *Operational* which contains an Assembly called *Function*. The internal architecture of the Assembly consists of two SWCs, called *SubFunction\_1* and *SubFunction\_2*, connected by two Connector elements, called *ConnectorData* and *ConnectorTrig*, for the data and the control flows, respectively. A TimingConstraint element is specified between the data output port of SubFunction\_1 and the data input port of SubFunction\_2.

## C. TIMING ANALYSIS

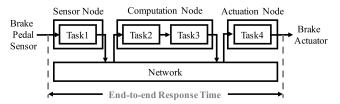

Many vehicular embedded systems are constrained by stringent timing requirements that must be satisfied during their development. End-to-end timing analysis is a well-established technique to verify the timing requirements that are specified on these systems. Such an analysis must be integrated to the tool chain that is used for the model- and component-based development of these systems. In order to support the timing analysis an appropriate system view, called end-to-end timing model, should be extracted from the software architecture of the system under analysis. The end-to-end timing model consists of two models, namely timing model and linking model. The timing model includes the timing properties (e.g., priorities, periods, worst- and

FIGURE 3. Example showing end-to-end response time.

best-case execution times, offsets and jitter) and timing requirements (e.g., deadlines and delay constraints) regarding all tasks, messages and task chains in the distributed embedded system. On the other hand, the information about links, dependencies, control flows (activation information) and data flows (information regarding data exchanges) among tasks and messages in all task chains are captured in the linking model. For example, consider a task chain shown in Figure 3. The chain is distributed over three nodes that are connected by a network. The system timing model includes all the timing information (discussed above) in the three nodes and the network. Whereas, the linking model includes all the linking information (discussed above) in the chain that initiates at Task1 in the Sensor Node and terminates at Task4 in the Actuation Node. It should be noted that the end-to-end timing model discussed above is in line with the classical timing model for distributed embedded system [14]-[16]. The analysis engines use the end-to-end timing model to analyse the timing behavior of the system. In this paper we consider the end-to-end timing analysis given in [15] and [17]. The analysis has been implemented in several industrial tools, e.g., [17]. The analysis results consist of response times of tasks and messages as well as system utilization. The analysis also calculates end-to-end response times and delays. The end-toend response time of a task chain is equal to the elapsed time

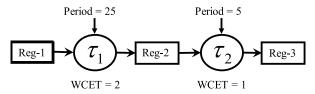

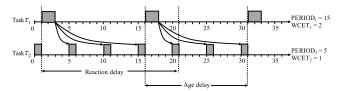

between the arrival of a stimulus, e.g., the brake pedal sensor input at the sensor node and the corresponding response, e.g., the brake actuation signal at the actuation node as shown in Figure 3. If the tasks in a chain are activated independently (e.g., by periodic clocks) then various types of end-to-end delays must also be computed to verify the timing behavior of the system. Age and Reaction are two such delays that are commonly found in vehicular embedded systems. The age delay in a task chain corresponds to the freshness of the data that is available at the output of the chain. This delay finds its importance in the control systems domain in vehicles. Whereas, the reaction delay in a task chain corresponds to the first reaction at the output of the chain for a given stimulus at the input of the chain. This delay finds its application in the body electronics domain in vehicles. In order to explain the age and reaction delays, consider a task chain in a single-node system as shown in Figure 4.

FIGURE 4. A task chain with independent activations of tasks.

The chain consists of two tasks, namely  $\tau_1$  and  $\tau_2$ . The tasks are activated by independent clocks of periods 25 milliseconds and 5 milliseconds respectively. Assume that the Worst-Case Execution Times (WCETs) of these tasks are 2 milliseconds and 1 millisecond respectively. Task  $\tau_1$  reads data from register Reg-1 and writes data to Reg-2. Similarly, task  $\tau_2$  reads data from Reg-2 and writes data to Reg-3. Since, the tasks are activated independently with different clocks, there can be multiple outputs (Reg-3) corresponding to any single input (Reg-1) to the chain as shown by several unidirectional arrows in Figure 5.

FIGURE 5. Example showing end-to-end delays.

The age and reaction delays are also identified in Figure 5. These delays are equally important in distributed embedded systems.

## D. PAPER CONTRIBUTIONS IN RELATION WITH AUTHORS' PREVIOUS WORK

In this work, we present MoVES, a model-driven methodology for real-time distributed vehicular systems on single- and multi-core, supporting the development and architectural exploration of system designs with temporal awareness. The methodology leverages the interplay of EAST-ADL

and RCM and consists of a fully automated mechanism defined in terms of a set of model transformations. RCM was originally thought for providing modelling purposes, but it did not feature a canonical definition of the language in terms of a metamodel. In [18], we reverse-engineered the RCM language and presented a preliminary metamodel definition of the RCM core elements. In [19], we provided a complete metamodel definition for RCM for modelling and timing analysis of vehicular embedded systems on singlecore. In [12] we extended the RCM metamodel definition for the development of vehicular systems on multi-core. This extension introduced modelling elements for the representation of the execution platform and the allocation information. In this paper, we leverage an even more enhanced version of the RCM metamodel definition given in [12], which includes the concept of application. Early timing verification is paramount in the vehicular domain. To this end, in [20] we proposed a mechanism for the exploitation of RCM timing capabilities at EAST-ADL design level. Such a mechanism leveraged the RCM metamodel definition given in [19] and consisted of a single model transformation for the generation of the RCM software architecture and timing properties from an EAST-ADL model, only. Moreover, the mechanism in [19] can not be applied for the development of vehicular embedded systems on multi-core. In this paper, by exploiting the new modelling capabilities of RCM, we introduce a methodology for the development of real-time distributed vehicular embedded systems on single- and multi-core, which guides the engineer to viable solutions with respect to timing requirements. To this end, the presented methodology leverages a refined version of the model transformation described in [20] and introduces i) four new model transformations for the automatic translation of the EAST-ADL FunctionalDesignArchitecture, HardwareDesignArchitecture and Allocation to RCM models and ii) a new model transformation that captures the timing analysis results and the corresponding RCM models and propagates them to the design level. Finally, we discuss the applicability of the proposed methodology by leveraging an industrial running example.

#### **III. THE MoVES METHODOLOGY: WHY?**

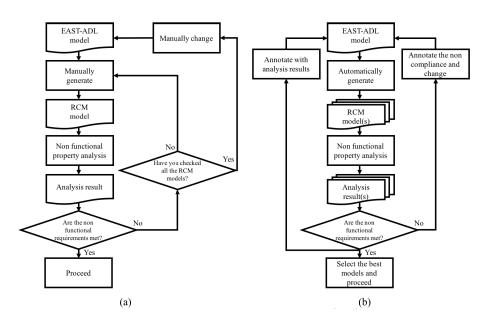

Among other factors, early verification of non functional requirements can positively affect the cost-efficiency of the software development for vehicular real-time embedded systems. Currently, early verification of non functional requirements is hard to achieve due to the lack of automation supporting models integration and analysis. For instance, let us consider a typical development process as described by the flowchart in Figure 6 (a).

As meaningful non functional analysis (such as timing) must be run on implementation models, the engineer is required to create a RCM model manually. The non functional analysis of interest is run on the manually created RCM model and the result is verified against the given set of non functional requirements. If the specified requirements are not met, the engineer is required to iterate the process and

FIGURE 6. Comparison between a development process without (a) and with MoVES (b).

modify or create a new RCM model until a compliant one is found. Since the process of creating and verifying implementation models is expensive, it is not leveraged early in the development process for having quick and early feedback on the design level models. To boost early verification, in this paper we propose MoVES, a novel model-driven methodology for the development of vehicular real-time embedded systems supporting early verification of non functional properties.

Let us consider a development process equipped with the proposed methodology as described by the flowchart in Figure 6 (b). In this setting, all meaningful RCM models are automatically generated from the design models and analysed by means of model transformations. Given a set of non functional requirements, model transformations are responsible for the selection and back propagation of the best RCM model (or set of models), too. Besides relieving the engineer from the manual and iterative definition of a RCM model, the proposed methodology enables early verification at design level. Moreover, while several iterations may be needed in the manual process to reach a RCM model that fulfils non functional requirements, MoVES is able to generate all meaningful RCM models and identify the best one(s) (as shown in Section VI) automatically in one single iteration.

## **IV. MoVES FOR TIMING**

Timing requirements are crucial for our domain of interest, vehicular real-time embedded systems, and that timing-related issues are typical problems arising very late in the development. For this reasons, in this work we discuss an instantiation of MoVES for supporting the development and architectural exploration of system-designs with temporal awareness.

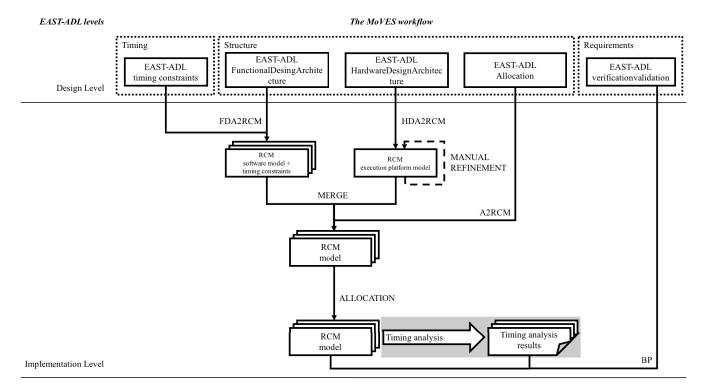

MoVES leverages the interplay of EAST-ADL and RCM and provides automation for their integration by means of six model transformations. Figure 7 gives a graphical representation of the methodology and its composing tasks.

The first step of the methodology is the automatic generation of the RCM models representing the software architecture and its timing properties at the implementation level. Such a generation process is characterised by a one-tomany mapping meaning that multiple RCM software models can be a valid translation of an EAST-ADL FucntionalDesignArchitecture, where each of the RCM model would entail different timing and control flow information. Within MoVES, this generation is entrusted to the FDA2RCM model transformation. In particular, starting from an EAST-ADL FucntionalDesignArchitecture complemented with EAST-ADL timing requirements, FDA2RCM generates, in a single execution, the set of the corresponding RCM software models equipped with RCM timing constraints as opposite to a manual generation considering only one specific solution. The second step of the methodology is the automatic generation of the RCM model representing the execution platform at the implementation level. This step is performed by the HDA2RCM model transformation which starts from an EAST-ADL HardwareDesignArchitecture and generates a corresponding RCM execution platform model. As RCM models the execution platform in a more detailed way than EAST-ADL (RCM employs the concepts of core and partition), the engineer can manually refine the generated RCM execution platform models. Detailed execution platform models are pivotal for the specification of the allocation information which, in turn, affects timing analysis. The third step of the methodology merges the RCM software and execution platform models into complete RCM models, where the

FIGURE 7. The MoVES and its composing tasks.

allocation information can be translated from the EAST-ADL Allocation. To this end, the MERGE model transformation is responsible for merging each generated RCM software model with the generated RCM execution platform model. The result is a set of complete RCM models. The fourth step of the methodology is the generation of the allocation information on the complete RCM models and it is entrusted to the A2RCM model transformation. In particular, A2RCM is responsible for the translation of the allocation information from an EAST-ADL Allocation model to the RCM complete models generated as a result of the MERGE transformation. Since RCM leverages a more fine-grained allocation mechanism than EAST-ADL, the methodology, by means of the ALLOCATION model transformation, is able to generate additional RCM allocation configurations that can not be derived from EAST-ADL. At this point, the RCM models contain all the information needed for the model-based timing analysis. Once the timing analysis is run, 6 the analysis results are produced and collected. The last step of the methodology is the back-propagation of the analysis results at the design level for enabling timing-aware design decisions and it is performed by the BP transformation. To this end, BP enriches the initial EAST-ADL model with the analysis results and the related RCM models such that the engineer can take timingaware design decision on the EAST-ADL models without creating or nor editing RCM models.

<sup>6</sup>The proposed methodology leverages model-based timing analysis. However, the analysis itself is not part of the contributions of this work. The interested reader can refer to [17] for further details.

In the following sections, we present a detailed discussion of each of the above mentioned model transformations. The complete implementation of the proposed methodology is available at http://www.mrtc.mdh.se/MoVES/.

## A. FDA2RCM

FDA2RCM is a one-to-many model-to-model transformation between EAST-ADL and RCM, which is realised in the Eclipse Modeling Framework (EMF)<sup>7</sup> using the Janus Transformation Language (JTL) [9]. JTL is a constraint-based bidirectional model transformation language specifically tailored to support non-determinism by generating all the possible target models in a single execution. Its implementation relies on the Answer Set Programming (ASP) [21], which is a type of declarative programming able to address hard (primarily NP-hard) search problems and based on the model (answer set) semantics of logic programming. The ASP solver is responsible to find and generate, in a single execution, all the possible target models that are consistent with the transformation rules following a deductive process. JTL adopts a QVTr-like syntax and allows a declarative specification of relationships between MOF models. It supports object pattern matching and automatically creates traces information to record what occurred during a transformation execution.

The FDA2RCM transformation is the starting point of the methodology and provides for the translation of the software architecture of the vehicular embedded system under

<sup>&</sup>lt;sup>7</sup>https://eclipse.org/modeling/emf/

development and its timing properties. An initial version of the FDA2RCM transformation is given in [20]. The proposed version i) extends the one in [20] with new rules for the translation of the EAST-ADL FunctionalDesignArchitecture elements into the RCM software elements composing the current RCM structural hierarchy (e.g., System, Application, etc.) and ii) replaces the logic constraints in the pre- and post-conditions of the transformation rules in favour of more compact and understandable transformation rules. In a nutshell, the FDA2RCM transformation is responsible for translating the elements of the EAST-ADL FunctionalDesignArchitecture to RCM software elements. In particular, it maps the EAST-ADL DesignFunctionPrototype, FunctionPort, FunctionConnector, AgeConstraint and ReactionConstraint elements to the RCM Assembly, SWC, Port, ConnectorData, DataAge and DataReaction elements, respectively. Additionally, the FDA2RCM transformation provides for the automatic generation of the RCM ConnectorTrig, Clock and Sink elements representing detailed control flow and timing information. As detailed control flow and timing information is not described in the EAST-ADL FunctionalDesignArchitecture, a single source EAST-ADL FunctionalDesignArchitecture can not be univocally translated in a single RCM model. For instance, the DFP2C and the DFP2CCS rules in Listing 1 define a non deterministic portion of the FDA2RCM transformation where a Design-FunctionPrototype element can be translated either to a SWC element or to a SWC element equipped with a Clock and a Sink element.

```

1transformation FDA2RCM(dl:designLevel, rcm:RubusMM) {

relation DFP2C {

name, id:String;

checkonly domain dl ps:designLevel::

DesignFunctionPrototype {

name = name,

id = id.

type = t:designLevel::DesignFunctionType {

isElementary = true

10

enforce domain rcm at:RubusMM::Assemblv {

11

12

circuit = c : RubusMM::Circuit {

name = name,

14

id = id

15

16

17

where { . . . }

18

19

relation DFP2CCS {

20

name, id:String;

checkonly domain dl ps:designLevel::

21

DesignFunctionPrototype {

22

23

24

enforce domain rcm at:RubusMM::Assembly {

25

circuit = c:RubusMM::Circuit {

26

name = name,

27

28

interface = i:RubusMM::Interface {...}

29

30

clock = clk:RubusMM::Clock {...},

sink = snk:RubusMM::Sink {...},

32

connectorTrig = con1:RubusMM::ConnectorTrig {...},

33

connectorTrig = con2:RubusMM::ConnectorTrig {...}

34

35

where { . . . }

```

LISTING 1. Fragment of the FDA2RCM model transformation in JTL.

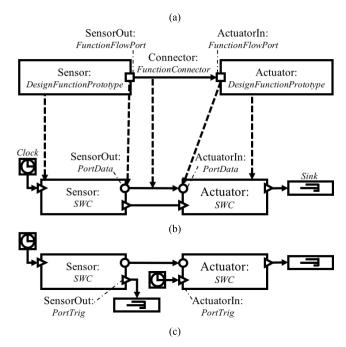

In this context, the JTL engine is able to generate, in a single execution, all the RCM software models entailing different and unique configurations of, e.g., SWC, Clock and Sink elements as opposite to a manual translation considering only a specific model. It is important to notice that, logic constraints can be applied for narrowing the space of the generated models. For instance, the execution of the FDA2RCM transformation to the source EAST-ADL model depicted in Figure 8 (a)<sup>8</sup> could be narrowed by means of logic constraints which could guide the generation of RCM models to those entailing valid configurations of SWC, Clock and Sink elements, only.

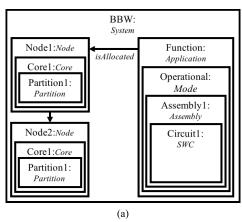

FIGURE 8. Example of simplified source and target models for the FDA2RCM transformation. (a) Source EAST-ADL model. (b) Target RCM model. (c) Target RCM model.

Accordingly, only the two RCM models in Figure 8 (b) and Figure 8 (c) would be generated. In the former, the SWC Actuator is activated from the SWC Sensor through the Connector Connector\_Trig, while in the latter it is activated by the independent Clock Clock\_Actuator.

#### B. HDA2RCM

HDA2RCM is a model-to-model transformation between EAST-ADL and RCM, which is realised by means of JTL. Together with the FDA2RCM transformation, HDA2RCM is the staring point of the methodology and provides automation means for the translation of the execution platform of the vehicular embedded system under development. In fact, execution platform models are pivotal for the specification of the allocation information which, in turns, affects timing analysis. Trivially, the over utilisation of a processor or a core can lead to timing deadline misses.

<sup>8</sup>For better understandability, we represent EAST-ADL and RCM models by means of a simplified graphical concrete syntax.

```

1transformation HDA2RCM(dl:designLevel, rcm:RubusMM) {

relation AtomicHardwareComponentPrototype2Node {

id, name: String;

checkonly domain dl hardwareComponentPrototype :

designLevel::HardwareComponentPrototype {

= id,

name = name.

type = hardwareComponentType : designLevel::Node {...}

10

11

enforce domain rcm system : RubusMM::System {

12

connectorNetwork = connectorNetwork : RubusMM::

ConnectorNetwork { },

13

node = node : RubusMM::Node

14

id = id.

15

name = name

16

core = core : RubusMM::Core {

17

18

partition = partition : RubusMM::Partition {...}

19

20

where {...}

23 1

```

LISTING 2. Fragment of the HDA2RCM model transformation in JTL.

FIGURE 9. Example of simplified source and target models for the HDA2RCM transformation. (a) Source EAST-ADL model. (b) Target RCM model.

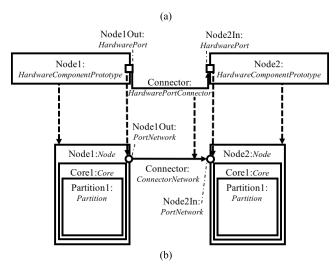

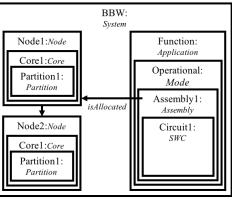

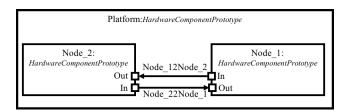

The HDA2RCM transformation is responsible for translating the EAST-ADL HardwareComponentPrototype elements to RCM execution platform elements. In particular, it maps the EAST-ADL Node, HardwarePortConnector and HardwarePort elements to the RCM Node, ConnectorNetwork and Port elements, respectively. As discussed in Section II, RCM models the execution platform with a structural hierarchy of elements consisting of Node, Core and Partition. However, EAST-ADL provides modelling element for the representation of Node elements, only. Therefore, in order to generate valid RCM models, the HDA2RCM transformation automatically generates, for each RCM Node element, a Core and a Partition element, too. Please note that, the engineer can still manually refine the generated RCM execution platform model, if needed. Listing 2 depicts an extract of the HDA2RCM transformation consisting of the transformation rule responsible for the generation of RCM Node, Core and Partition elements. Figure 9 depicts an example of an execution of the HDA2RCM model transformation. In particular, the EAST-ADL model depicted in Figure 9 (a) and consisting of two connected Node elements, Node1 and Node2, is translated into the RCM model depicted in Figure 9 (b) consisting of two connected Node elements, Node1 and Node2, containing a Core and a Partition element each.

#### C. MERGE AND A2RCM

MERGE and A2RCM are two model-to-model transformations realised within EMF using the QVT Operational (QVT-O) language [22]. Query/View/Transformation (QVT) is a standard set of model transformation languages defined by the Object Management Group and it is composed by three model transformation languages, which are QVT-O, QVT Relations and QVT Core. QVT-O is an imperative language especially designed for writing unidirectional model transformations when declarative model transformations are hard to specify due to the absence of direct correspondence between elements of the source and target models. Thereby, a QVT-O model transformation explicitly specifies the steps to execute in order to generate a target model starting form a source one.

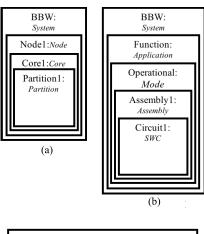

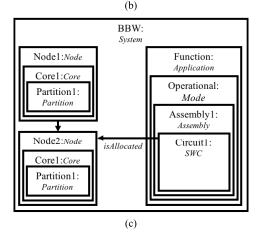

Once the FDA2RCM and the HDA2RCM transformations are run, a set of RCM software models and one RCM execution platform model are produced. In this context, the MERGE transformation is responsible for merging a RCM software model to the RCM execution platform model with the purpose of creating a complete RCM model where the allocation information can be translated and refined. In a nutshell, the MERGE transformation performs a weaving of the RCM models, where the modelling elements of the RCM execution platform model are linked to the System element of the RCM software model through its Node reference. Let us consider the RCM execution platform and software models depicted in Figure 10 (a) and Figure 10 (b), respectively. The former consists of a System element called BBW containing a Node element called Node1, which contains a Core element Core1. Eventually, Core1 contains a Partition element called Partition1. The latter consists of a System element called BBW, which in turns contains an Application element called Function. Function contains a Mode element called Operational, which contains an Assembly element called Assembly1. Assembly1 contains a SWC called Circuit1. Accordingly, the application of the MERGE transformation would produce the RCM model depicted in Figure 10 (c) where the RCM execution platform elements in Figure 10 (a) are integrated into the RCM software model in Figure 10 (b) by means of the Node reference of the System BBW element. A2RCM is an inplace transformation [23] which follows the MERGE transformation and it is responsible for translating the allocation information from the EAST-ADL Allocation to each of the RCM models generated from the MERGE transformation. Allocation information is crucial for the model-based timing analysis as, e.g., the over utilisation of a node or a core element can result in violating the timing requirements. As discussed in Section II, in EAST-ADL the allocation

FIGURE 10. Example of simplified source and target models for the MERGE transformation. (a) Source RCM execution platform model. (b) Source RCM software model. (c) Target RCM model.

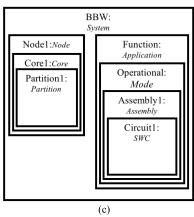

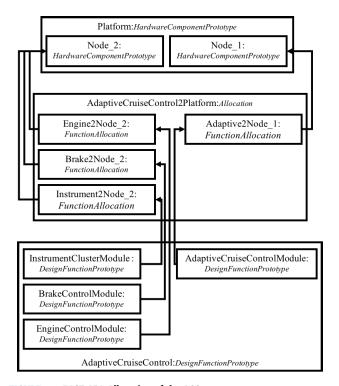

information is modelled by means of a set of Function Allocation elements which links the DesignFunction-Prototype element to the HardwareComponentPrototype element. For instance, the Function Allocation Allocation1 in Figure 11 (a) allocates the DesignFunctionPrototype Function to the HardwareComponentPrototype Node1. In RCM, the allocation information is specified by means of the is Allocated reference of the Allocatable elements. Therefore, the A2RCM transformation is responsible for setting the RCM is Allocated references according to the EAST-ADL Function Allocation elements. For instance, if we apply the A2RCM model transformation to the EAST-ADL Allocation depicted in Figure 11 (a), we obtain the RCM model in Figure 11 (b). Accordingly, the isAllocated reference of the Application element called Function is set to the Node element called Node1.

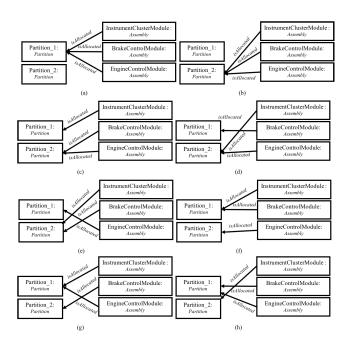

#### D. ALLOCATION

ALLOCATION is a one-to-many, in-place model transformation on the RCM language realised by means of JTL. As discussed in Section II, compared to EAST-ADL, RCM leverages a more fine-grained structural hierarchy for the modelling of the execution platform and the allocation. In particular, within RCM, any Allocable element (Function, Mode,

FIGURE 11. Example of a simplified source and target models for the A2C transformation. (a) Source EAST-ADL model. (b) Target RCM model.

Assembly and SWC) can be allocated to any of the Allocator element (Node, Core and Partition). Due to the different granularity between RCM and EAST-ADL, complete allocation information can not be directly translated from an EAST-ADL Allocation. In this context, the ALLOCATION transformation provides automation means for the generation of the allocation information in the RCM models when a direct translation from EAST-ADL is not possible. In other words, the ALLOCATION transformation automatically generates the isAllocated reference of the RCM Allocatable elements and sets it to any of the RCM Allocator elements. As there can be several allocation strategies, the engineer is required to express a choice over the preferred one. This can be done by toggling the comments on the transformation rules which realise the desired allocation strategy (e.g., Assembly to Core, Assembly to Partition, SWC to Core, etc.).. Based on the user choice, the ALLOCATION transformation is able to generate, in a single execution, all the RCM models which entail different and unique allocation configurations. Similarly to the FDA2RCM, logic constraints can be applied for narrowing the number of the generated RCM models. This is particularly useful when partial allocation information is already available (as in case of, e.g., legacy vehicular systems) or for discarding specific allocation configurations.

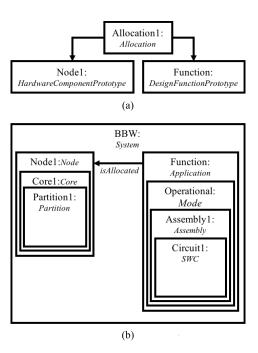

Listing 3 shows a fragment of the ALLOCATION transformation which depicts the transformation rule responsible for allocating the Assembly element to Node element. Accordingly, the JTL engine generates, in a single execution, all the RCM models entailing different combinations of Assembly to Node elements. That is, the application of the ALLOCATION transformation to the RCM model depicted in Figure 12 (a) generates the two RCM models depicted in Figure 12 (b)

```

Itransformation ALLOCATION(source: RubusMM, target: RubusMM) {

relation Assembly2AllocatedAssemblyNode{

name, id: String;

checkonly domain source as:RubusMM::Assembly {

name

id = id

10

11

enforce domain target at:RubusMM::Assembly {

12

name = name,

13

id.

isAllocated = n:RubusMM::Node {...}

15

16 }

17 }

```

LISTING 3. Fragment of the ALLOCATION model transformation in JTL.

and Figure 12 (c). In the former, Assembly1 is allocated to Node1, while in the latter Assembly1 is allocated to Node2.

#### E. BP

BP is an in-place, text-to-model transformation on the EAST-ADL metamodel realised by means of OVT-O. Within MoVES, BP is the last step for unveiling the RCM models and their related analysis results at the design level thus for enabling timing-aware design decisions. In fact, once the RCM model and the analysis results are unveiled at design level, the engineer can easily grasp the compliance of the starting EAST-ADL models to the specified timing requirements. Even further, she can select the most appropriate RCM model, among the compliant ones, for proceeding with the development process. The BP transformation uses the EAST-ADL VVCase modelling element from the Requirement package. In particular, it automatically creates the VVLog and VVActualOutcome modelling elements for the given VVCase element and sets their attribute Date, ID and Name. Moreover, the BP transformation is responsible for setting the Text attribute of the EAST-ADL VVACtualOutcome element with the URLs of the folders containing the timing analysis results and the related RCM models.

#### V. CASE STUDY

In this section, we demonstrate the usability of MoVES by developing the adaptive cruise control system as an extension of the cruise control system. The cruise control system is a vehicular feature which allows the vehicle to keep a steady speed to the value provided by the driver. To this end, it employs (at least) 4 modules: one for communicating/controlling the engine, one for communicating/controlling the brakes, one for communicating with the driver's instrument cluster and one for the computation. However, the traditional cruise control system does not take into account traffic information such as presence of other vehicles or obstacles. The Adaptive Cruise Control (ACC) system is a vehicular feature which allows a vehicle's cruise control to adapt the vehicle's speed to the surrounding environment. More precisely, once the user sets a target speed and a time gap for the vehicle, a radar detects slow-moving vehicles or other obstacles

FIGURE 12. Example of simplified source and target models for the ALLOCATION transformation. (a) Source EAST-ADL model. (b) Target RCM model. (c) Target RCM model.

that are in the path of the vehicle. In case an obstacle or a slower vehicle is detected, the ACC system slows down the vehicle or brakes to keep the desired distance between the ACC vehicle and the obstacle or the forward vehicle, where the distance is calculated as a function of the specified time gap and the speed of the vehicle. When the ACC system detects that the forward vehicle or the obstacle is no longer in the vehicle's path, it speeds up the vehicle to maintain the cruise speed set by the driver. With respect to the cruise control functionality, the ACC enhances the computation module with functionalities which provide the adaptive features.

FIGURE 13. Block diagram of the ACC system.

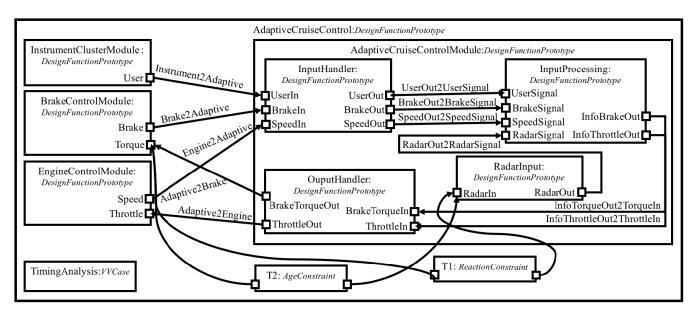

Figure 13 shows a block diagram of the ACC system<sup>9</sup> that is adapted from [24].

The InstrumentClusterModule is responsible for collecting the user's inputs, such as speed and time gap, and for sending them to the AdaptiveCruiseControlModule. The EngineControlModule and the BrakeControlModule are responsible for sending the information regarding speed and braking of the vehicle to the AdaptiveCruiseControlModule, respectively. AdaptiveCruiseControlModule is the core of the ACC feature and it is responsible for calculating the acceleration and the braking of the vehicle in the presence of forward vehicles or obstacles. In particular, the InputHandler software component is responsible for acquiring and processing the inputs coming from the other modules and to forward them to the InputProcessing software component. Similarly, the RadarInput software component is responsible for acquiring and processing the information coming from the radar and forwarding it to the InputProcessing software component. Based on the user inputs on the cruise mode and considering the presence of a forward obstacle, the InputProcessing software component is responsible for computing the decision whether the vehicle has to slow down, speed up or keep a steady speed. It communicates this information to the OutputHandler software component which, in turn, is responsible for sending the related brake torque and throttle signal to the BrakeControlModule and EngineControlModule, respectively.

According to MoVES, the development starts from an EAST-ADL FucntionalDesignArchitecture, HarwareDesignArchitecture and Allocation models. Figure 14 depicts an extract of the EAST-ADL FucntionalDesignArchitecture for the ACC. In the remainder of this section, for the sake of verbosity, we adopt a simplified concrete syntax both for the EAST-ADL and RCM models and omit some modelling elements if of no interest for the discussion.

The modules and their inner architecture are represented by means of the DesignFunctionPrototype and FunctionFlowPort elements. For instance, the RadarInput software component is represented by means of the RadarInput DesignFunctionPrototype element and the RadarIn and RadarOut FunctionFlowPort elements. The connections among software components and modules are represented by means of FunctionConnectorelements connecting the FunctionFlowPort elements. Fo instance, the RadarInput

and InputProcessing DesignFunctionPrototype elements are connected by means of the RadarOut2RadarIn FunctionConnector connecting the RadarOut and RadarSignal FunctionFlowPorts. In addition to the architectural elements, two timing constraints, denoted by Reaction Constraint T1 and Age Constraint T2, and VVCase element, denoted by TimingANalysis, are specified. According to these constraints:

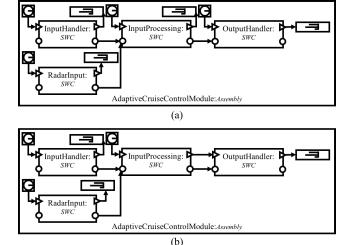

The reaction and age delays between the arrival of the radar signal at the input of the InputProcessing software component and its delivery to the BrakeControlModule shall not exceed 25 and 15 milliseconds, respectively. Starting from the EAST-ADL FucntionalDesignArchitecture in Figure 14, MoVES automatically generates RCM software models. In particular, RCM System, Application and Mode elements, namely AdaptiveCruiseControl, Adaptive-CruiseControl and AdaptiveCruiseControl\_Operational are generated. The AdaptiveCruiseControlModule, EngineControlModule, BrakeControlModule and InstrumentCluster-Module DesignFucntionPrototype elements are translated into RCM Assembly elements while the InputHandler, Radar-Input, InputModeControl, Processing and Outputhandler DesignFunctionPrototype elements are translated into RCM SWCs. PortData, ConnectorData and TimingConstraint elements are generated from the EAST-ADL FunctionFlow-Port, FunctionConnector and TimingConstraint elements, respectively. Due to the lack of control flow information in EAST-ADL, RCM PortTrig, ConnectorTrig, Clock and Sink elements are automatically generated by the FDA2RCM.

However, as there might be multiple ways of specifying these elements, this generation produces four RCM software models each of which entails different and unique combinations of RCM PortTrig, ConnectorTrig, Clock and Sink elements. For instance, let us consider the activation of the OutputHandler SWC in the two RCM models in Figure 15. In the RCM model in Figure 15 (a), the OutputHandler SWC is triggered by an independent clock whether in the RCM model in Figure 15 (b) it is triggered by its predecessor, Input-Processing. Within MoVES, the second step is the translation of the EAST-ADL HardwareDesignArchitecture model representing the execution platform architecture. Figure 16 depicts the EAST-ADL HardwareDesignArchitecture for the ACC feature.

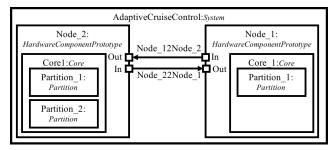

It is realised by means of two Node elements, Node\_1 and Node\_2, each of which represents a MPC560XP microcontroller that is a single-core microcontroller for vehicular and industrial safety applications. <sup>10</sup> Two HardwarePortConnector elements, Node\_12Node\_2 and Node\_22Node\_1, realise the communication between the two nodes. Starting from the EAST-ADL HardwareDesignArchitecture in Figure 16, MoVES generates the RCM model depicted in Figure 17.

In particular, the EAST-ADL Node and HardwarePort-Connector elements are translated into RCM Node and

<sup>&</sup>lt;sup>9</sup>The interested reader can access the full ACC case study implementation at http://www.mrtc.mdh.se/MoVES/.

<sup>&</sup>lt;sup>10</sup>http://www.nxp.com/products/automotive-products/microcontrollers-and-processors/32-bit-power-architecture/ultra-reliable-mpc56xx-32-bit-automotive-industrial-microcontrollers-mcus/ultra-reliable-mpc560xp-mcu-for-automotive-industrial-safety-applications:MPC560xP

FIGURE 14. EAST-ADL FunctionalDesignArchitecture of the ACC system.

**FIGURE 15.** Two of the four RCM software models of the ACC system. (a) RCM software model for the ACC system. (b) RCM software model for the ACC system.

FIGURE 16. EAST-ADL HardwareDesignArchitecture of the ACC system.

NetworkConnector elements. According to the HDA2RCM transformation, the inner architecture of each generated RCM model is enriched with a Core and a Partition element. That is, Core\_1 and Partition\_1 elements are generated for the RCM Node\_1 and Node\_2 elements. Eventually, by means

FIGURE 17. RCM execution platform model of the ACC system.

of manual refinements, an additional Partition element, Partition\_2 is added to the RCM Node\_2. At this point, MoVES merges the RCM software and execution platform models and the result is a set of four complete RCM models where the allocation information from the EAST-ADL Allocation can be translated. To this end, Figure 18 depicts the EAST-ADL Allocation model for the ACC feature.

The EAST-ADL Allocation model consists of four FunctionAllocation elements mapping AdaptiveCruise-ControlModule to Node\_1 and InstrumentClusterModule, EngineControlModule and BrakeControlModule to Node\_2. Accordingly, MoVES translates the allocation information on the RCM models resulting from the MERGE transformation. Figure 19 depicts one example of RCM model along with the translated allocation information. Consequently, the isAllocated references of the InstrumentClusterModule, BrakeControlModule and EngineControlModule assemblies are set to the Node\_2 element while the isAllocated reference of the AdaptiveCruiseControlModule Assembly elements is set to the Node\_1 element. However, as EAST-ADL does not leverage the concepts of cores and partitions for the modelling of the execution platform, the allocation of the

FIGURE 18. EAST-ADL Allocation of the ACC system.

FIGURE 19. RCM model for the ACC system with the allocation information.

InstrumentClusterModule, EngineControlModule and Brake-ControlModule elements can not be refined with respect to core and partition elements of Node\_2. Nevertheless, such an information can be automatically generated from the ALLOCATION transformation as described in Section III. In particular, for the ACC system, we decided to choose an allocation strategy which allocates Assembly to Partition elements. Consequently, as there are 8 different ways to allocates the three Assembly elements to the two Partition elements, MoVES generates a final set of 32 RCM models (8 refined RCM models for each of the 4 RCM models

FIGURE 20. RCM models for the ACC system with the refined allocation information.

resulting from the A2C). Eight of the 32 final RCM models are depicted in Figure 20.

At this point, model-based timing analysis is run on each of the generated 32 RCM models with the aim of verifying whether the specified reaction and age constraints are met. Table 1 summarises the results of the timing analysis. Table 1 summaries the analysis results for the 32 generated RCM models. It can be seen that, out of the 32 RCM models of the ACC system, only 16 RCM models satisfy the specified age and reaction constraints. In particular, MoVES is able to automatically identify the 5 RCM models with the best timing performances. In this respect, it is important to note that MoVES can be easily constrained for notifying the engineer only with the best RCM models rather than with all the compliant ones. Eventually, the VVLog and VVActualOutcome elements are created for the VVCase TimingAnalysis. Moreover, the attribute Text of the VVActualOutcome is set to the URLs of the folders containing the generated RCM models and their analysis results. At this point, the engineer can select any of the 16 RCM models satisfying the specified age and reaction constraints and continue with the synthesis of the code for the target platform.

#### VI. DISCUSSION AND VALIDATION

In this work, we introduced a novel model-driven methodology, MoVES, for the software development of real-time distributed vehicular embedded systems on single- and multi-core platforms. Considering the importance of timing, the proposed methodology supports the development and architectural exploration of system-designs with temporal awareness. To this end, MoVES leverages the interplay of two domain-specific modelling languages, EAST-ADL and RCM, and provides a fully automated mechanism for the

TABLE 1. Age and reaction delay analysis results.

|       | _ ~            |                |

|-------|----------------|----------------|

| RCM   | Calculated     | Calculated     |

| Model | Age Delay      | Reaction Delay |

| ID    | (microseconds) | (microseconds) |

| 1     | 21630          | 31170          |

| 2     | 21380          | 30920          |

| 3     | 21480          | 31020          |

| 4     | 21380          | 30920          |

| 5     | 21730          | 31270          |

| 6     | 21380          | 30920          |

| 7     | 21380          | 30920          |

| 8     | 21380          | 30920          |

| 9     | 11810          | 21810          |

| 10    | 11560          | 21560          |

| 11    | 11660          | 21660          |

| 12    | 11560          | 21560          |

| 13    | 11910          | 21910          |

| 14    | 11560          | 21560          |

| 15    | 11560          | 21560          |

| 16    | 11560          | 21560          |

| 17    | 11690          | 21690          |

| 18    | 11440          | 21440          |

| 19    | 11540          | 21540          |

| 20    | 11440          | 21440          |

| 21    | 11790          | 21790          |

| 22    | 11440          | 21440          |

| 23    | 11440          | 21440          |

| 24    | 11440          | 21440          |

| 25    | 21630          | 31170          |

| 26    | 21380          | 30920          |

| 27    | 21480          | 31020          |

| 28    | 21380          | 30920          |

| 29    | 21730          | 31270          |

| 30    | 21380          | 30920          |

| 31    | 21380          | 30920          |

| 32    | 21380          | 30920          |

|       |                | 30,20          |

Specified Age Constraint: 15000 microseconds Specified Reaction Constraint: 25000 microseconds

= satisfied = best

generation of the RCM models containing detailed software, execution platform, timing and allocation information for schedulability analysis. EAST-ADL has been developed by the automotive industry and its consortium includes several international automotive companies such as McLaren, Volvo, FIAT, Hyundai, etc. The validation of the applicability and correctness of EAST-ADL is outside the scope of this work, however, the interested reader, can refer to [3]. The RCM metamodel definition exploited in this work is an extension of the previous definition given in [12]. Through the years the applicability and correctness of RCM has been verified against several industrial system designs such as i) the Intelligent Parking Assist (IPA) System [25] (consisting of 2 Node elements and 42 SWCs), ii) the simplified IPA system [26]

(consisting of 2 Node elements and 7 SWCs), iii) the Steerby-wire System [20] (consisting of 1 Node and 6 SWCs) and the Brake-by-wire System [12] (consisting of 3 Node elements and 14 SWCs). Additionally, its industrial relevance has been acknowledged by our industrial partners (e.g., Volvo CE, BAE Systems, etc.) through several national and international projects [27], [28].

The automation mechanism, core of the MoVES methodology, is realised by means of a suite of six model transformations. In this respect, the case study presented in Section V helps in discussing some interesting properties of the model transformations, such as syntactic and semantic correctness, complexity, termination and performance. With the term syntactic correctness, we refer to the ability of a transformation to produce valid target models when executed on valid source models [29]. Such a property holds for transformations leveraged in MoVES and the interested reader can easily check the validity of the generated RCM models by accessing the MoVES implementation<sup>11</sup> With the term semantic correctness, we refer to the ability of a transformation to produce semantically valid target models [29]. In this respect, it is important to note that none of the transformations within MoVES suffer of information loss. That is, they consist of a precise and finite set of rules for mapping EAST-ADL to RCM elements without altering, violating or colliding the structural hierarchies of the languages. Eventually, the semantic of the generated RCM models was validated by the leveraged schedulability analysis. We consider two dimensions for the transformations' complexity. The first dimension of the transformations' complexity refers to the complexity of the generated RCM models. In this respect, it is important to note that the transformations always generate RCM models of equal complexity of manually defined RCM models. The second dimension of the transformations' complexity refers to the size of the generated set of RCM models. All the leveraged model transformations, except FDA2RCM and ALLOCATION, are one-toone. For the FDA2RCM transformation, if we set n as the number of the software functions enclosed by the timing constraints, then FDA2RCM would generate a maximum of  $2^{(n-1)}$  RCM models. For instance, in the case of the ACC feature, despite the EAST-ADL FunctionalDesignArchitecture models 9 software functions, the FDA2RCM generates only 4 RCM models as the specified age and reaction constraints enclose 3 software functions. It is important to remark that, as discussed in Section V, logic constraints can be applied for reducing the number of the generated RCM models by discarding those models which entails configurations of timing and control elements that are known to be not relevant. For the ALLOCATION transformation, if we set k as the number of RCM Allocator elements and n as the number of the RCM Allocated elements, then ALLOCATION would generate a maximum of  $k^{(n)}$  RCM models. For instance, in the case of the ACC feature, we decided to proceed with an

<sup>11</sup> http://www.mrtc.mdh.se/MoVES/

allocation strategy assigning the n = 3 RCM Assembly to the k = 2 Partition elements. Accordingly, a total number of 8 RCM models containing unique allocation configurations was generated. Similar to FDA2RCM, logic constraints can be specified for narrowing the generation process. For instance, let us consider the case in which we are not interested in the RCM models containing allocation configuration where the EngineControlModule Assembly is not allocated to the Partition\_2. In other words, we fix the allocation of the EngineControlModule Assembly to the Partition 2. In this case, ALLOCATION would generate only 4 RCM models. Trivially, the transformations' complexity can affect the termination and performance properties. Although providing formal proof on these properties was outside the scope of the work, the case study showed that all the transformation terminate in few seconds.<sup>12</sup>

We believe that MoVES discloses the opportunity to improve the cost-efficiency of software development process by means of i) automation and ii) reduced need for late modifications on the software. In particular, automation by means of model transformations allows to cut the development time while ensuring the compliance with the non functional requirements of the vehicular embedded software. Without MoVES, in fact, the software development would progress incrementally with team of engineers manually defining implementation models until a suitable one, from a non functional perspective, is found. On the contrary, by adopting MoVES, the implementation models would be automatically generated and non functional requirements verified at once allowing the engineers to focus and reason only on the compliant ones. Kurt-Lennart Lundbäck, CEO of Arcticus Systems, on the use of MoVES:

"I feel that autonomous vehicles on multi-core platforms are introducing a lot more of complexity and concerns. In this domain, automation can be a game-changer. For us, as a tool and technology providers, it would be particularly beneficial to have automated support for things like 'allocation' for reducing the complexity of our tool suite, Rubus ICE, and improve its usability. For our customers, this can result in lower development effort and improved confidence in the quality of the software under development."

It is important to note that MoVES does not introduce accidental complexity in the software development process. In fact, it is true that setting up the methodology might require an additional effort, but it is a one-time-effort as opposed to manual processes always requiring constant effort. Moreover, the engineer would have to deal only with the set of RCM models satisfying the non functional requirements which, as shown in Section V for timing, is a limited number (5 out of the 32 generated RCM models). By allowing early verification, MoVES discloses the opportunity of reducing late modifications on the vehicular embedded software, which empirical studies showed to be up to 40 times more

expensive than same modifications during the design of the software [6]. In fact, by using MoVES, the engineer is either notified on the non compliance of the starting EAST-ADL models to the set of the considered non functional requirements or notified with the set of the compliant RCM models with which proceed for the development. In the former scenario, late modifications are prevented while in the latter they are not needed.

In this article, MoVES is presented by specifically targeting timing properties, given the paramount relevance of these properties in the design and development of vehicular embedded systems. Nonetheless, there are further non functional properties that play an important role during the development of these systems, namely memory usage, energy efficiency, and so forth. In this respect, it is worth to note that the methodology proposed by MoVES can be instantiated to consider these and other properties, as long as they are measurable and comparable at the EAST-ADL and RCM levels of detail. Additionally, other properties can be exploited for comparing multiple RCM models having equally good timing performance and selecting the best available RCM model solution. Moreover, further non functional properties could be considered from the initial stages of the proposed workflow to be integrated and used during the generation process of the possible solutions. In both cases, the MoVES would need to be extended only in terms of specific model transformations for the generation of the related non functional properties of interest.

## **VII. RELATED WORK**

This article deals with several research problems, here grouped as development of vehicular software systems, development of multi-core systems, and support for design-space exploration. In the remainder of this section, for each of the mentioned problems relevant related works are discussed.

#### A. DEVELOPMENT OF VEHICULAR EMBEDDED SYSTEMS

The growing complexity of nowadays vehicular software demands adequate approaches for its effective development. AUTOSAR [4] is an industrial initiative to provide a standardised software architecture for the development of vehicular software systems. The timing model for AUTOSAR was developed in the TIMMO and TIMMO2USE projects [30], [31]. In these projects, a framework was developed to specify the end-to-end timing constraints and analyse the corresponding end-to-end delays [15], [32], [33]. In general, AUTOSAR is not meant to be used in isolation, but plays the role of the implementation level as e.g. prescribed by the EAST-ADL. Even if the layered structuring of EAST-ADL entails abstraction and separation-of-concerns in the development, there is no specific automation support for interconnecting the different layers. As a consequence, the results of analysis performed at lower levels of abstraction, e.g. by means of AUTOSAR, have to be manually tracked back to higher levels, e.g. design models. More in general, the discontinuities in the development process due to the

$<sup>^{12}\</sup>mbox{The}$  case study was run on a 1,7 GHz Intel Core i7 processor, with 8 GB 1600 MHz DDR3 memory.

abstraction gaps between the different layers have to be tackled manually by the developer. This task can be timeconsuming and error-prone, especially when considering the complexity of modern vehicular systems [34]. On the contrary, in this article we propose to leverage automation through model transformations to keep the consistency between the different abstraction levels. The abstraction gaps naturally introduce non-determinism, which is managed by an appropriate transformation language (JTL). Multi-core architectures are part of the AUTOSAR standard since version 4.0. However, AUTOSAR does not distinguish between the control and the data flows at the application software level, a distinction that is fundamental for providing early timing verification [35]. Moreover, AUTOSAR does not provide means for modelling the execution platform [36]. These issues motivate our choice of using RCM as the implementation level for EAST-ADL and the MoVES methodology. CHESS is a cross-domain framework for the design of component-based embedded systems, including vehicular systems [37]. It is based on a combination of different languages, like MARTE and SYSML, which gave birth to a specific UML profile. The framework provides modelling of embedded software for early analysis, such as dependability and schedulability, as well as for code generation, monitoring, and back-propagation. Currently, the CHESS framework does not provide design-space exploration, nor it supports uncertainty in the development process. Vehicular systems are often referred to as cyber-physical systems (CPS) [38], especially when considering autonomous driving and networks of vehicles (fleets). Several approaches deal with CPS development by adopting multi-paradigm modelling techniques and leverage simulation mechanisms to perform early analysis of systems [39], [40]. Even if the analyses presented in this article do not exploit simulation techniques, the MoVES methodology does not prevent the use of simulation mechanisms to analyse and select the generated design alternatives with respect to quality attributes of interest.

## B. DEVELOPMENT OF EMBEDDED SYSTEMS