### UNIVERSITÀ DEGLI STUDI DELL'AQUILA dipartimento di ingegneria industriale e dell'informazione e di economia (diiie)

Dottorato di Ricerca in Ingegneria Industriale e dell'Informazione e di Economia Curriculum in Ingegneria elettrica, elettronica e dell'informazione XXXIII ciclo

# Development of circuits and systems for optical data links in biomedical applications

SSD ING-INF/01

Dottorando

### Guido Di Patrizio Stanchieri

### (M. 255068)

Coordinatore del corso Prof. Giuseppe Ferri Tutor Prof. Andrea De Marcellis

### Summary

| ABSTRACT                                                                                | 8           |

|-----------------------------------------------------------------------------------------|-------------|

| INTRODUCTION                                                                            | 9           |

| 1. DATA LINK SYSTEMS – STATE OF THE ART                                                 | 13          |

| 2. OPTICAL DATA LINK – DESIGN AND IMPLEMENTATION                                        | 25          |

| 2.1. Design and implementation - discrete components solution                           |             |

| 2.1.1. FPGA implementation of a digital architecture for data pre-processing and UWB co | ding 28     |

| 2.1.2. Analogue conditioning circuits for lasers and photodiodes                        | 29          |

| 2.1.3. FPGA implementation of a digital architecture for UWB data decoding and post-pro | ocessing 32 |

| 2.1.4. Experimental setup and measurements                                              | 35          |

| 2.2. Design and implementation – CMOS integrated solution                               | 41          |

| 2.2.1. Design of a digital architecture for UWB data coding                             |             |

| 2.2.2. Design of conditioning circuits for lasers and photodiodes                       |             |

| 2.2.3. Design of a digital architecture for UWB data decoding                           | 47          |

| 2.2.4. Experimental setup and measurements                                              | 50          |

| 2.2.5. Full Custom design of integrated photodiodes                                     | 55          |

| 2.2.5.1. Design, analysis and simulations – TSMC 0.18µm CMOS Technology                 | 56          |

| 2.2.5.2. Design, analysis and measurements – AMS 0.35µm CMOS Technology                 | 60          |

| 3. OPTICAL DATA LINK - APPLICATIONS                                                     | 63          |

| 3.1. Event-driven serial communication on optical fiber for the humanoid robot iCUB     | 63          |

| 3.2. Tactile sensory feedback system based on UWB optical link for prosthetics          | 67          |

| 4. IMPROVED SOLUTION FOR WIRELESS OPTICAL DATA LINKS                                    | 72          |

| 4.1. System Design, Analysis and Simulations                                            | 73          |

| 4.2. System Implementation and Experimental Results                                     |             |

| CONCLUSION                                                                              | 86          |

| REFERENCES                                                                              | 88          |

| APPENDIX A: FPGA IMPLEMENTATION OF A TRUE RANDOM NUMBERS GENERATO                       | R 91        |

| I. Analysis of the main seeds of entropy for TRNG implementations                       |             |

| II. Overall architecture of the designed TRNG                                           |             |

| III. Experimental results                                                               | 100         |

| APPENDIX B: ANALOGUE FRONT-END CIRCUITS FOR BIOMEDICAL APPLICATIONS.                    |             |

| I. Transimpedance amplifier                                                             | 109         |

| II. Current-to-frequency converter                                                      | 111         |

| III. Capacitance-to-frequency converter                                                 | 114         |

| APPENDIX C: OPTICAL WIRELESS POWER TRANSFER                                             |             |

| I. System design                                                                        |             |

| II. Simulation Results                                                                  | 119         |

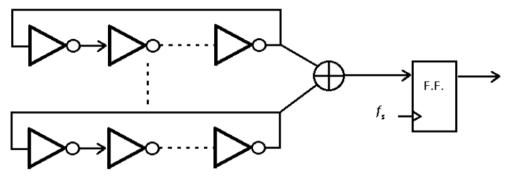

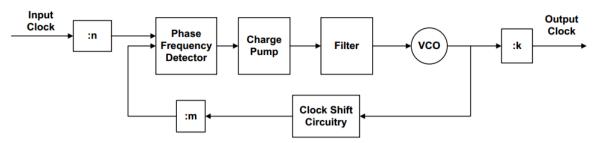

| APPENDIX D: CLOCK DUTY-CYCLE CORRECTION IN INTEGRATED DIGITAL SYSTEM                    | 4S 123      |

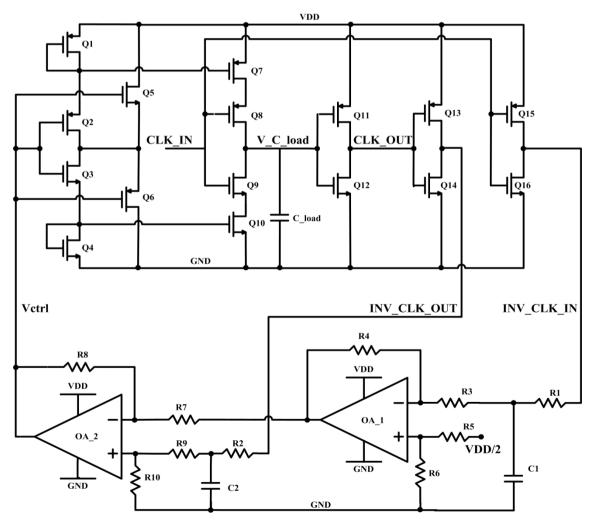

| I. Circuit Design                                                                       | 124         |

|                                                                                         |             |

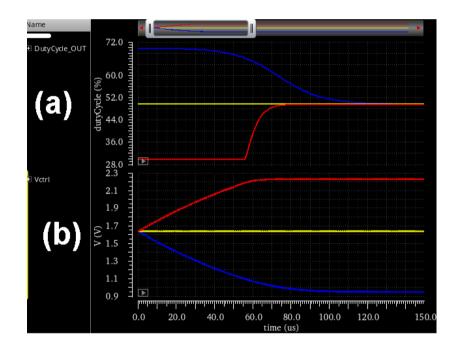

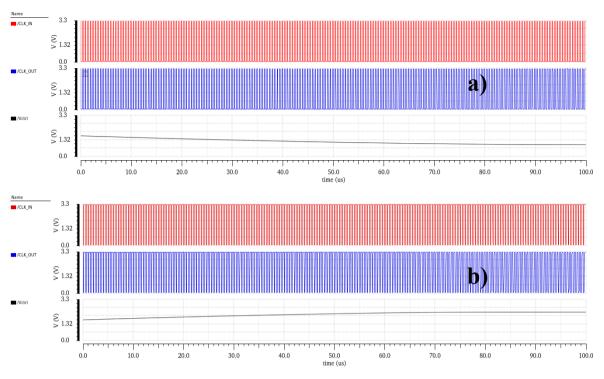

| II.  | Circuit Analysis and Simulations                                                                  | 126 |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | NDIX E: TUNABLE-GAIN DUAL-CHANNEL DUAL-PHASE LOCK-IN AMPLIFIER FOR<br>R TRANSMISSION SPECTROSCOPY | 131 |

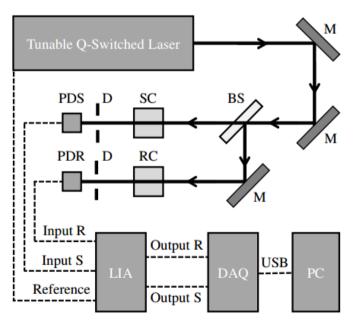

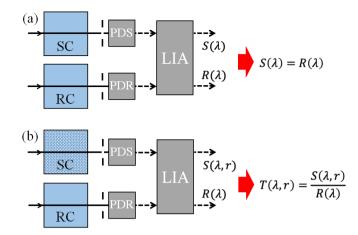

| I.   | LTS Methodology                                                                                   | 132 |

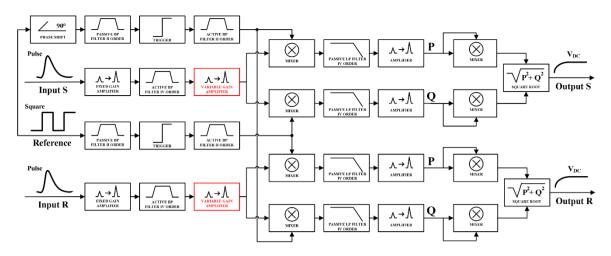

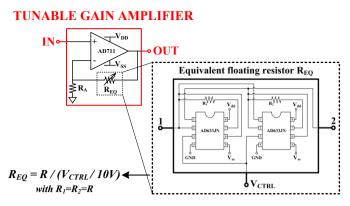

| II.  | Tunable-Gain Dual-Channel Dual-Phase Lock-In Amplifier (LIA)                                      | 134 |

| III. | Experimental Measurements with the Overall System                                                 | 138 |

| PUBB | BLICATIONS                                                                                        | 140 |

# List of Figures

| Figure 1 - The block diagram of a generic biotelemetry system                                                   | 13 |

|-----------------------------------------------------------------------------------------------------------------|----|

| Figure 2 - Absorption spectra of human skin constituents.                                                       | 17 |

| Figure 3 – Modulation techniques commonly used in biomedical devices.                                           | 17 |

| Figure 4 - Principle of ASK modulation                                                                          |    |

| Figure 5 - Principle of FSK modulation.                                                                         | 19 |

| Figure 6 - Principle of PSK modulation.                                                                         | 19 |

| Figure 7 – The detailed block diagram of a NFC communication system.                                            | 20 |

| Figure 8 – Data coding algorithm of a pulsed Manchester encoding                                                | 21 |

| Figure 9 - Block diagram of an optical transcutaneous link.                                                     | 21 |

| Figure 10 - Electronic interfaces of (A) the internal device and (B) the external device of an optical          |    |

| transcutaneous link.                                                                                            | 22 |

| Figure 11 - Block diagram of a bidirectional optical transcutaneous link                                        | 22 |

| Figure 12 - Scattering, absorption and reflection of an optical signal in human skin                            | 23 |

| Figure 13 – Block diagram of an IR-UWB transmitter architecture (on the left) and some related                  |    |

| experimental results (on the right).                                                                            | 23 |

| Figure 14 - Timing diagram showing the data coding process using an S-OOK modulation                            | 25 |

| Figure 15 – Block scheme of the developed transcutaneous optical biotelemetry system                            |    |

| Figure 16 - Pre-processing circuit, implemented on FPGA, showing the organisation of the different contro       |    |

| units (CUs) for the data acquisition system.                                                                    |    |

| Figure 17 - Digital logic scheme of the Data Coding block.                                                      | 29 |

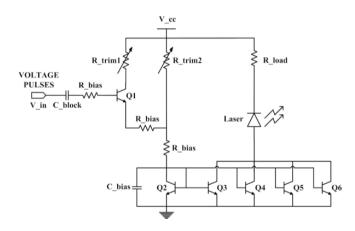

| Figure 18 - Schematic circuit for the laser biasing and driving.                                                | 30 |

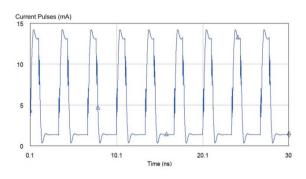

| Figure 19 - Simulation of the sequence of driver generated output current pulses                                | 30 |

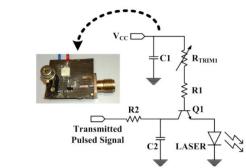

| Figure 20 – Schematic circuit of the laser driver and its PCB implementation                                    | 31 |

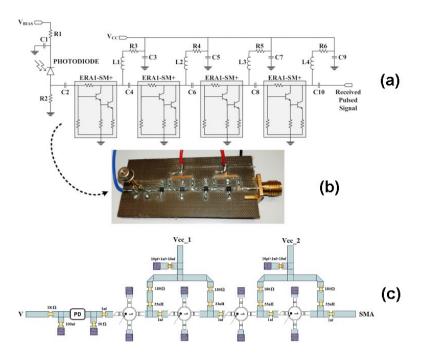

| Figure 21- Schematic of the photodiode conditioning circuit (a), its PCB implementation (b) and PCB layor       | ut |

| (c)                                                                                                             |    |

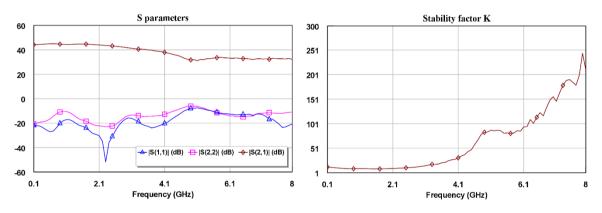

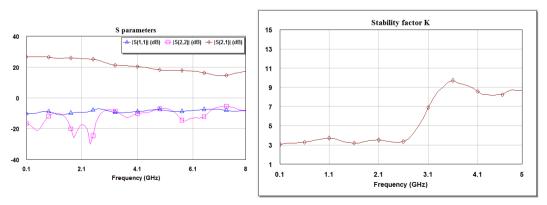

| Figure 22 - S parameters and stability factor K of the transimpedance amplifier.                                | 32 |

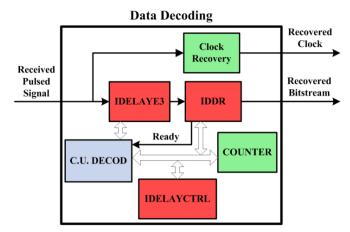

| Figure 23 - Data decoding circuit, implemented on FPGA, that recovers also the clock signal.                    | 33 |

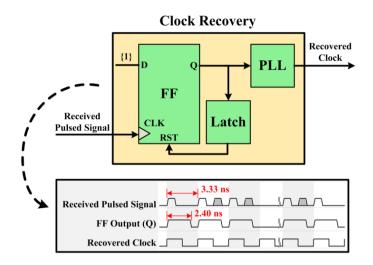

| Figure 24 - Clock recovery circuit, implemented on FPGA, that recovers a symmetrical clock from the             |    |

| received pulse stream                                                                                           | 34 |

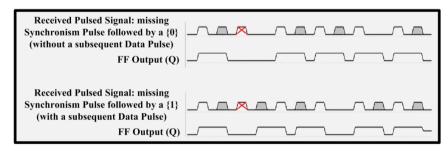

| Figure 25 - Example showing the impact of transmission errors in the clock recovery circuit.                    | 34 |

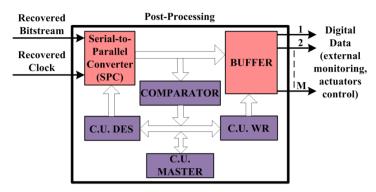

| Figure 26 - Post-processing circuit, implemented on FPGA, that recovers the individual channel data             | 35 |

| Figure 27 - Top-level system architecture of the implemented optical biotelemetry (Unit Under Test)             |    |

| completed by the test system.                                                                                   | 36 |

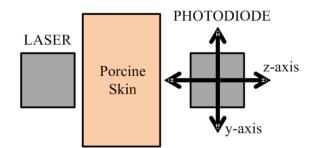

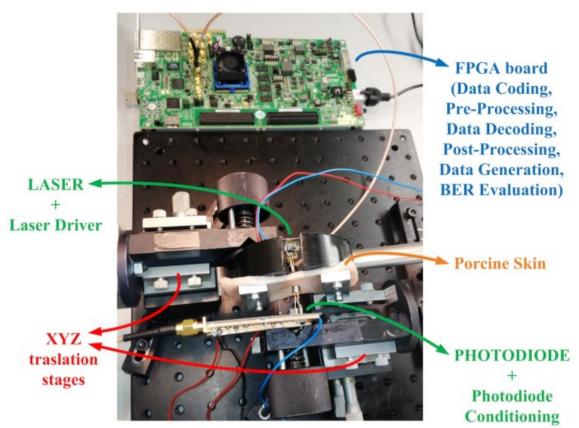

| Figure 28 - Schematic of the experimental setup for characterizing the optical biotelemetry showing the         |    |

| relative position of the transmitter (the VCSEL Laser), of the tissue (the porcine skin), and the receiver (the | Э  |

| photodiode) mounted on an XYZ translation stage for precise adjustment.                                         | 37 |

| Figure 29 - Experimental setup for characterizing the developed optical biotelemetry system.                    | 38 |

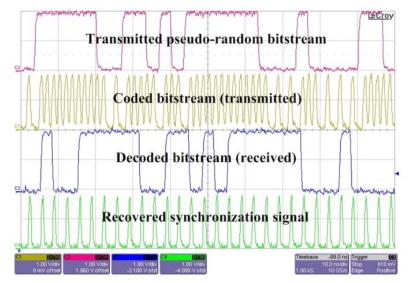

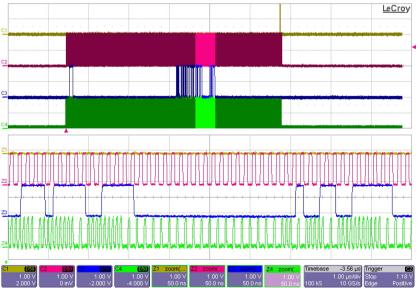

| Figure 30 - Experimental measurement: main signals during the transmission of a true random bitstream at        |    |

| 300 Mbps. The waveforms reported from top to bottom refer to: (in purple) the input bitstream of true           |    |

| random data; (in yellow) the transmitted coded pulses; (in blue) the decoded data; (in green) the recovered     |    |

| clock signal.                                                                                                   |    |

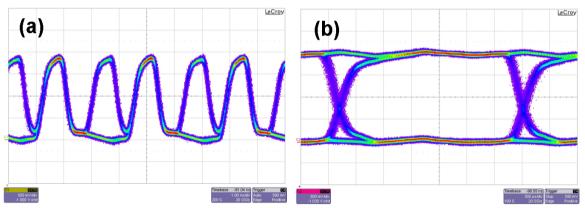

| Figure 31 - Multiple acquisitions of the transmitted (a) and eye-diagram (b) of the received signal (i.e., the  |    |

| recovered bitstream).                                                                                           | 39 |

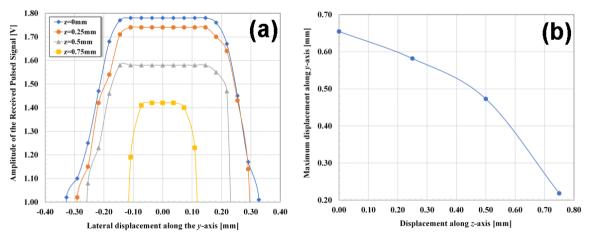

| Figure 32 - Optical link sensitivity to lateral misalignment between the VCSEL and the photodiode (a);                                                       |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| receiver spatial operability range in terms of the maximum possible lateral displacement between the VCS                                                     |      |

| and the photodiode (b)                                                                                                                                       |      |

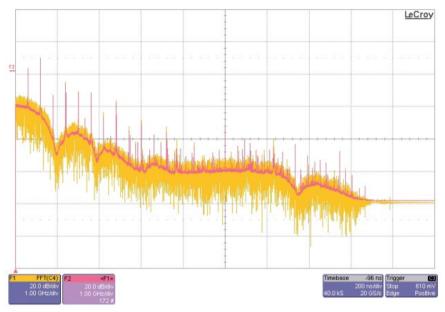

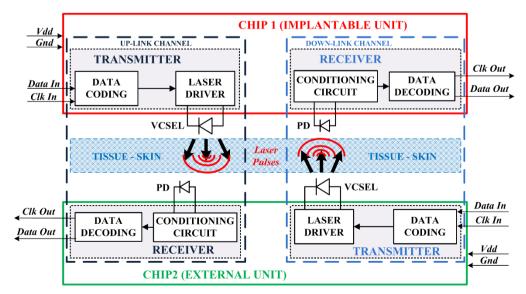

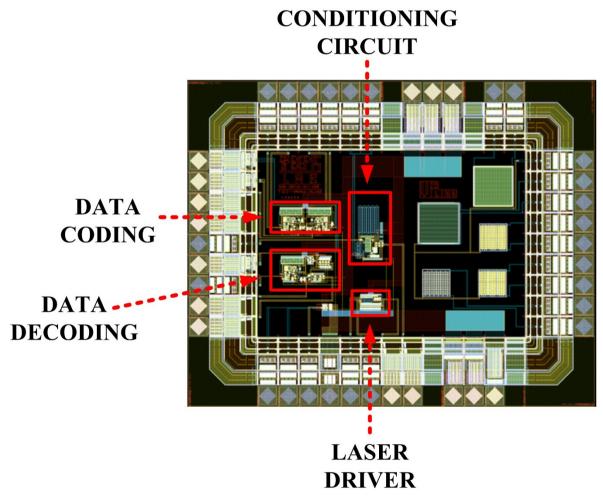

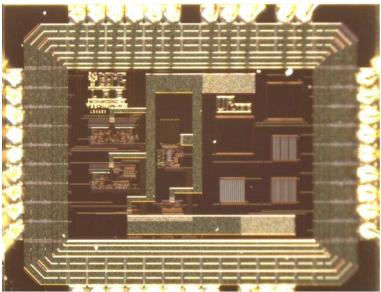

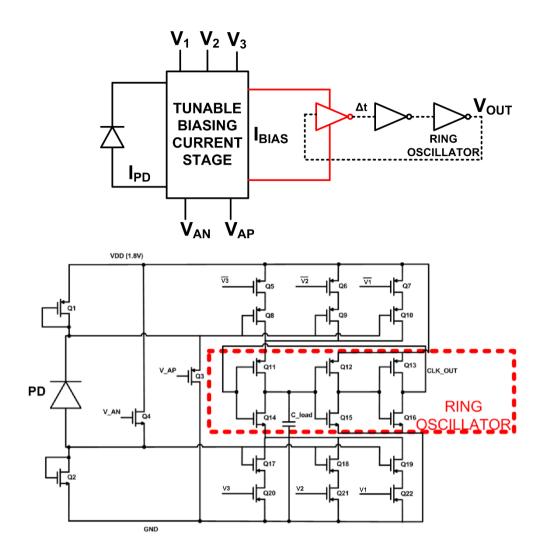

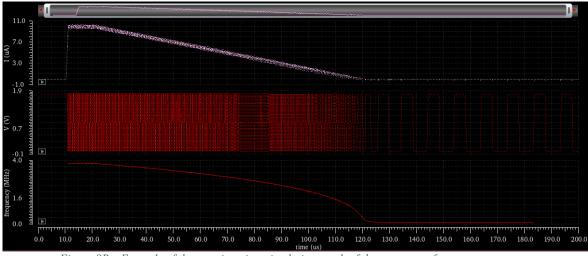

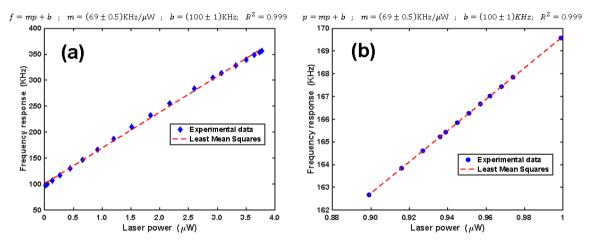

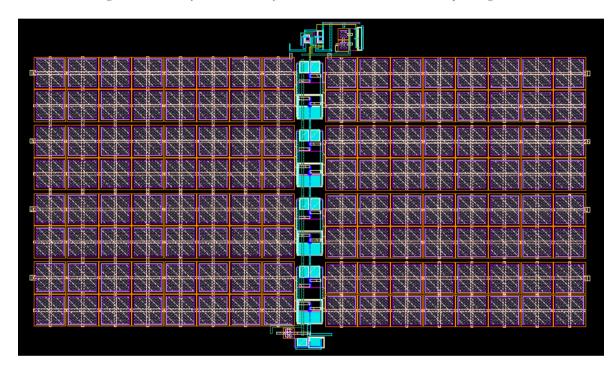

| Figure 33 - Power spectrum of the transmitted pulse signal<br>Figure 34 - Block scheme of the implemented IC for optical data link in biotelemetry systems   |      |

| Figure 35 - Complete layout design of the optical biotelemetry system.                                                                                       |      |

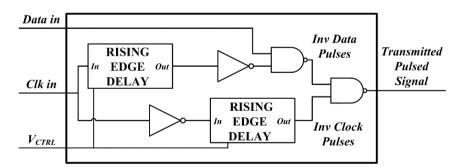

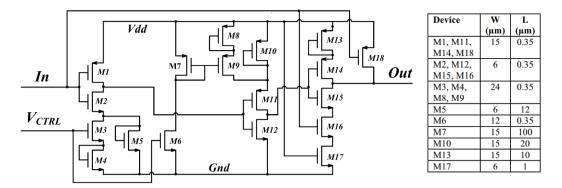

| Figure 36 - The architecture at block scheme level of the full-custom DATA CODING block                                                                      |      |

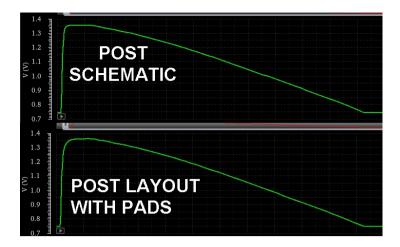

| Figure 37 - Schematic circuit at transistor level of the RISING EDGE DELAY block.                                                                            |      |

| Figure 38 - Post layout simulation of the Rising Edge Delay block.                                                                                           |      |

| Figure 39 - Post layout simulation of the Data Coding block                                                                                                  |      |

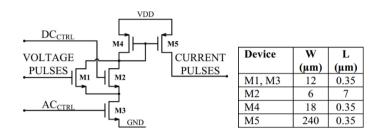

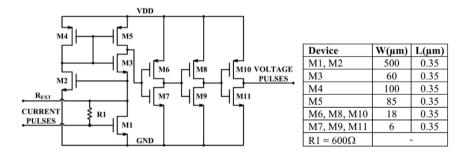

| Figure 40- Schematic circuit of the laser driver                                                                                                             | . 46 |

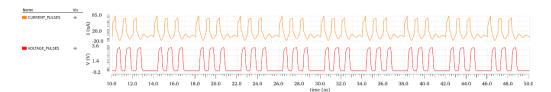

| Figure 41 - Simulation result related to the transient response of the laser driver circuit                                                                  |      |

| Figure 42 - Schematic of the photodiode interface circuit                                                                                                    |      |

| Figure 43 - Simulation result showing the transient time response of the photodiode interface circuit                                                        |      |

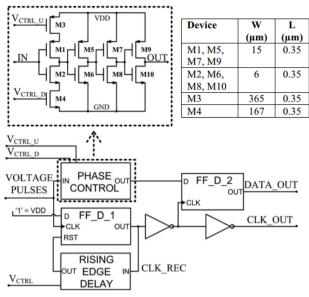

| Figure 44 - Circuit schematic of the digital decoding block                                                                                                  |      |

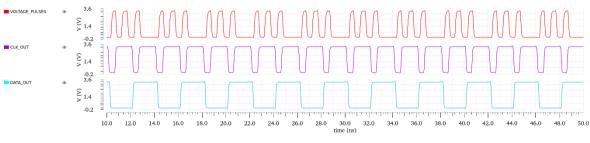

| Figure 45 - Simulation result of the Data Decoding block.                                                                                                    |      |

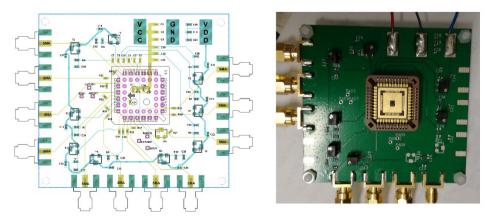

| Figure 46- Microphotograph of the fabricated ASIC<br>Figure 47 - Layout and photo of the fabricated PCB for the chip experimental test, characterization and | . 30 |

| measurements                                                                                                                                                 | 50   |

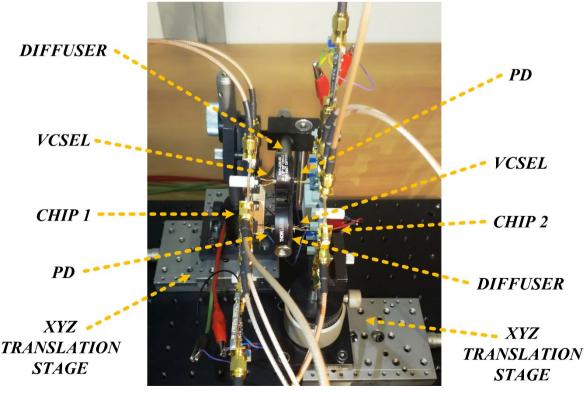

| Figure 48 - Experimental setup used for the ASIC characterization                                                                                            |      |

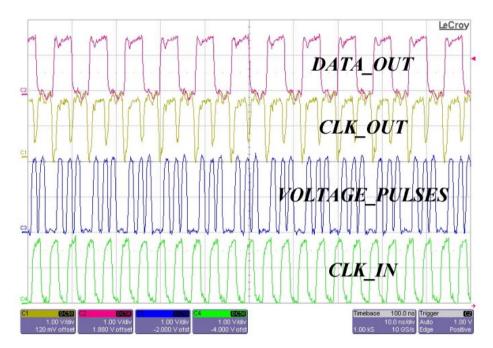

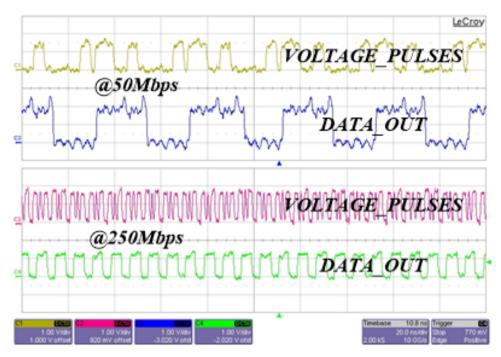

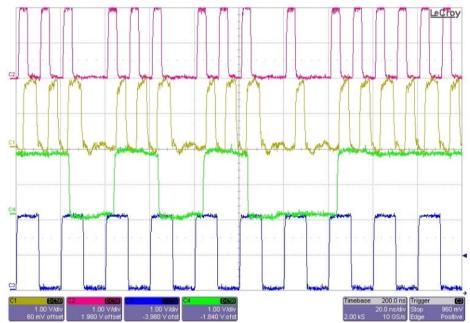

| Figure 49 - Experimental measurement: main signals related to a communication channel operating at 250                                                       |      |

| Mbps and transmitting a repeated {0,1} bitstream                                                                                                             | . 52 |

| Figure 50 - Measured signals related to a bidirectional communication link operating at 250 Mbps (uplink                                                     |      |

| channel) and 50 Mbps (downlink channel) transmitting a repeated {0,1} bitstream                                                                              |      |

| Figure 51 - Comparison between the coded signal generated by the FPGA board and by the developed ASI                                                         |      |

|                                                                                                                                                              |      |

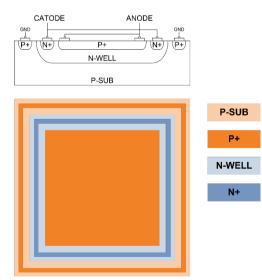

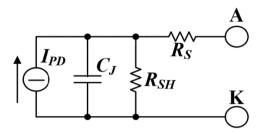

| Figure 52 - PD structure.                                                                                                                                    |      |

| Figure 53 - PD simplified electrical model.                                                                                                                  |      |

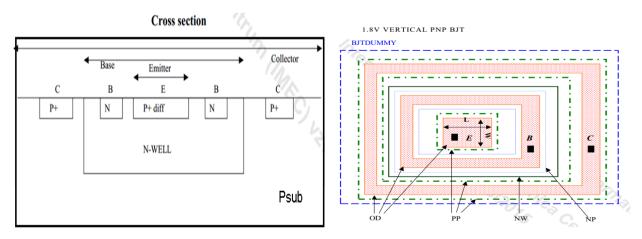

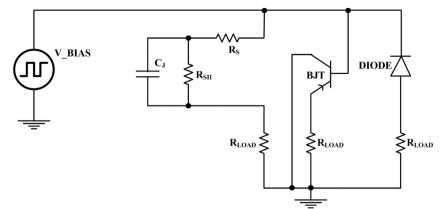

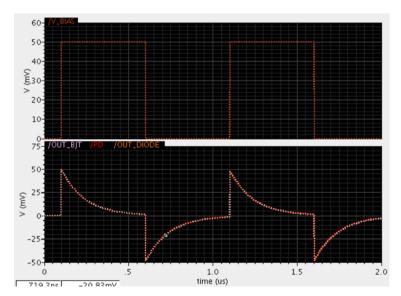

| Figure 54 - PNP BJT layout from TSMC 180 nm library<br>Figure 55 - Comparison between a simplified PD model, a TSMC BJT component and a TSMC Diode           | . 30 |

| component.                                                                                                                                                   | 57   |

| Figure 56 - Comparison between the response of a simplified PD model, a TSMC BJT component and a                                                             |      |

| TSMC Diode component (bottom picture) respect a square wave input (on top).                                                                                  | . 57 |

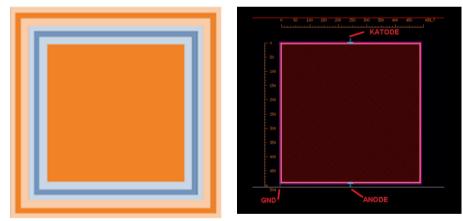

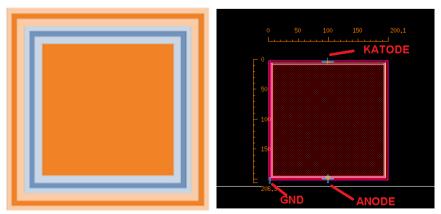

| Figure 57 - PD Layout, PNP junction of 500x500 µm2 (0.25 mm2) for optical power transfer applications.                                                       |      |

| Figura 58 - PD Layout, PNP junction of 200x200 µm2 (0.04 mm2)                                                                                                | . 58 |

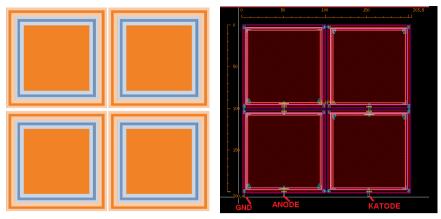

| Figure 59 - Layout of four PNP junction of 100x100 µm2 each connected in series (0.04 mm2)                                                                   |      |

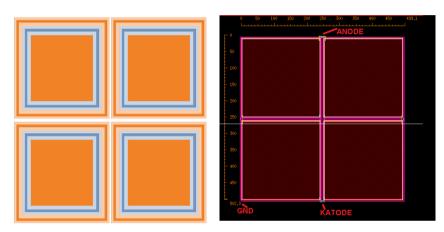

| Figure 60 - Layout of four PNP junction of 100x100 µm2 each connected in parallel (0.04 mm2).                                                                |      |

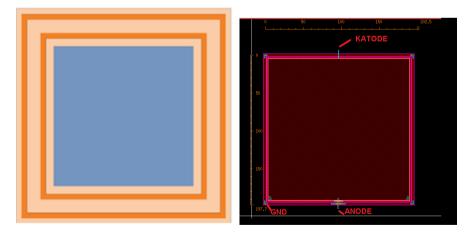

| Figure 61 - PD Layout, NP junction of 200x200 µm2 (0.04 mm2).                                                                                                |      |

| Figure 62 - PD Layout, roost structure PNP junction of 200x200 µm2 (0.04 mm2) [33].                                                                          |      |

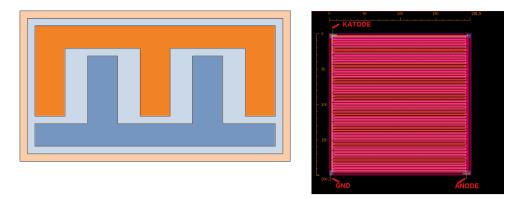

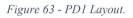

| Figure 63 - PD1 Layout<br>Figure 64 - PD2 Layout                                                                                                             |      |

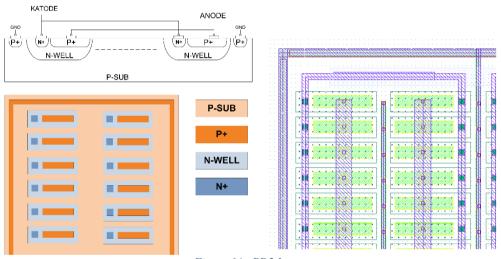

| Figure 65 - Experimental setup: (a) PD connected in photovoltaic mode and (b) PD connected in                                                                | . 01 |

| photoconductive mode                                                                                                                                         | 61   |

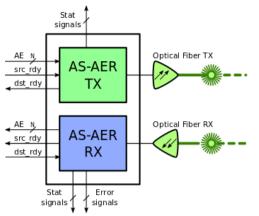

| Figure 66 – Overall block diagram of the reference implementation of the transceiver for the developed IB                                                    |      |

| AS-AER protocol.                                                                                                                                             |      |

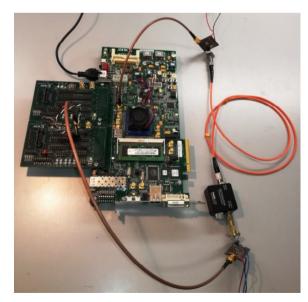

| Figure 67 - Photo of the experimental set-up implemented for testing the optical fiber communication link.                                                   | . 65 |

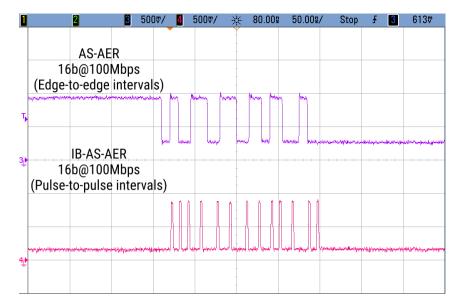

| Figure 68- Main signals related to the implemented IB-AS-AER serial protocol operating with 16 bit per                                                       |      |

| event at 100Mbps                                                                                                                                             |      |

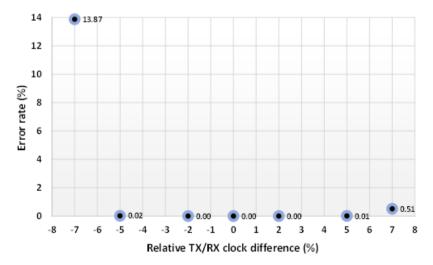

| Figure 69 - Error rate as a function of the relative difference between TX and RX clocks.                                                                    |      |

| Figure 70 - Overall implementation scheme of a data communication system for prosthetic devices                                                              |      |

| Figure 71 - PD and conditioning circuit.                                                                                                                     |      |

| Figure 72 - S parameters and stability factor K of the photodiode conditioning circuit<br>Figure 73 – Structure/composition of the serial data package       |      |

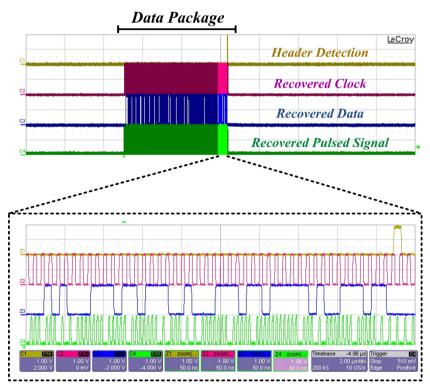

| Figure 74 - Experimental measurement: main signals related to the receiver                                                                                   |      |

| Figure 75 - Experimental measurement: main signals related to the receiver, events detected only by few                                                      | . 70 |

| sensors                                                                                                                                                      | . 70 |

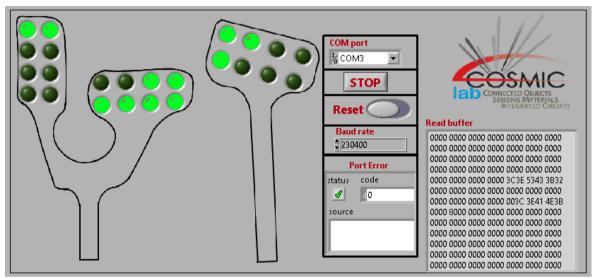

| Figure 76 - GUI for graphical data representation.                                                                                                           |      |

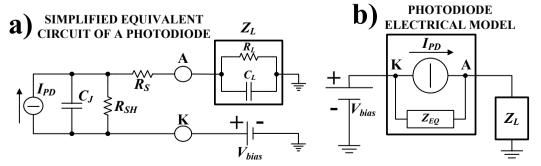

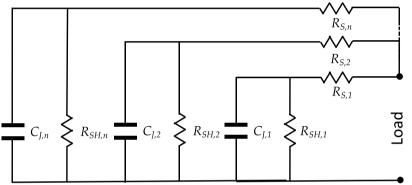

| Figure 77 - Panel a): Equivalent circuit of a photodiode where CJ, RSH and RS are the internal capacitance                                                   |      |

| the shunt resistance and the series resistance, respectively. Panel b): electrical current model of a photodiod                                              |      |

| where ZEQ and ZL are the equivalent and ex.                                                                                                                  |      |

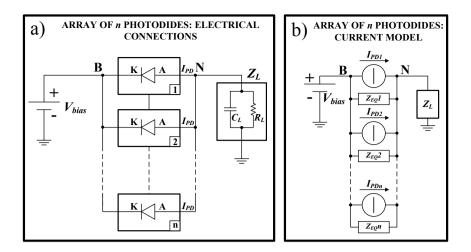

| Figure 78 - Panel a): the electric scheme chosen to add the currents IPD generated by N different PD in the                                                  |      |

| Kirchhoff node N: K and A are the PD cathode and anode, respectively; RL are the load resistors. Panel b)                                                    |      |

| the current model of an array of n-photodiodes                                                                                                               |      |

|                                                                                                                                                              | 4    |

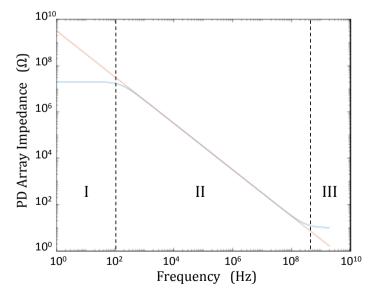

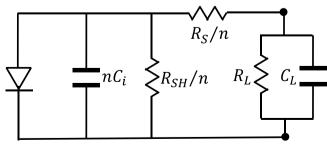

| Figure 79 - The equivalent circuit of the array of n PD as seen from the load terminals<br>Figure 80 - The behaviour of the total impedance respect to the load terminals as a function of the frequence                               |          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| of the current generated by an array of n=5 PD. Refer to the text for the description of the three regions                                                                                                                             |          |

| indicated in the plot.                                                                                                                                                                                                                 | 15       |

| Figure 81 - The equivalent circuit of an array of n PDs connected.                                                                                                                                                                     |          |

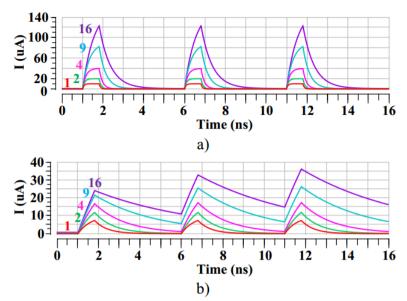

| Figure 82 - The output current pulses at the Kirchhoff node N of Figure 1 as a function of the number of the                                                                                                                           |          |

| connected PD: a) FDS015 photodiode; b) FDS010 photodiode.                                                                                                                                                                              |          |

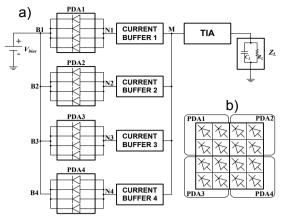

| Figure 83 - Panel a): the block scheme for the connection of the 4 sub-arrays PDA1, PDA2, PDA3, PDA4.                                                                                                                                  |          |

| The current pulse generated by each one of the subarrays is buffered before to be added at the Kirchhoff no                                                                                                                            |          |

| M and amplified by a TIA. Panel b): the final array.                                                                                                                                                                                   | /9       |

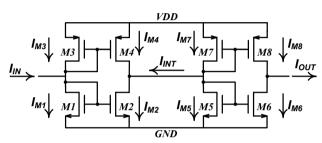

| Figure 84 - The schematic of the current buffer employed in Figure 83 designed in the AMS 0.35µm standa                                                                                                                                |          |

| CMOS technology.                                                                                                                                                                                                                       |          |

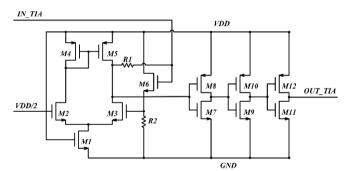

| Figure 85 - The schematic of the TIA designed in AMS 0.35µm standard CMOS technology                                                                                                                                                   |          |

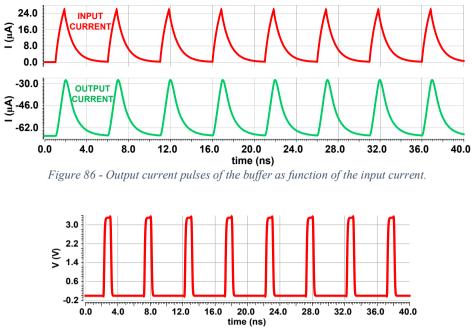

| Figure 86 - Output current pulses of the buffer as function of the input current.                                                                                                                                                      |          |

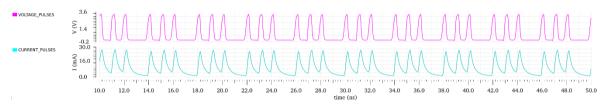

| Figure 87 - The voltage pulsed output amplified by the TIA at a repetition rate of 200MHz                                                                                                                                              | 81       |

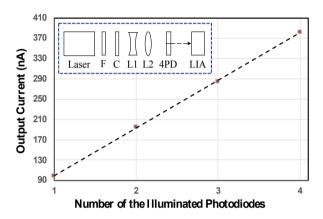

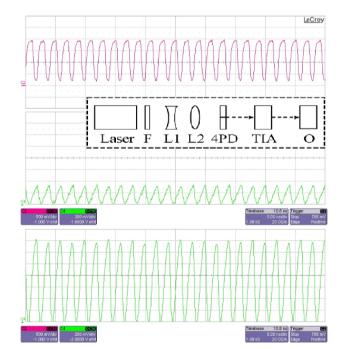

| Figure 88 - The output current as a function of the number of the illuminated PD forming the 2x2 array at low frequency rate. In the inset the entirel set up used for the measurements, the loser is a 10 mW output                   |          |

| low frequency rate. In the inset the optical set-up used for the measurements: the laser is a 10 mW output power CW HeNe; F is a neutral density filter to suitably attenuate the laser power; L1 and L2 form a                        |          |

|                                                                                                                                                                                                                                        |          |

| telescopic lens system used to magnify the laser spot for a uniform illumination of all the PD forming the 2 array; LIA is the lock-in amplifier.                                                                                      |          |

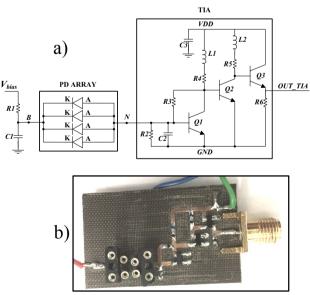

| Figure 89 - The TIA schematic realized by using high frequency large bandwidth RF commercial                                                                                                                                           | 02       |

| components (a) and its physical realization (b)                                                                                                                                                                                        | on       |

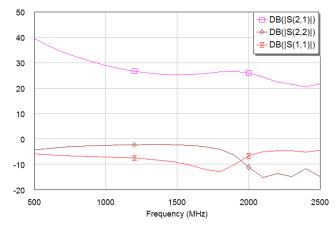

| Figure 90 - Evaluation of the S parameters S(2,1), S(2,2) and S(1,1) of the implemented TIA.                                                                                                                                           |          |

| Figure 90 - Evaluation of the S parameters 5(2,1), 5(2,2) and 5(1,1) of the implemented TTA.                                                                                                                                           |          |

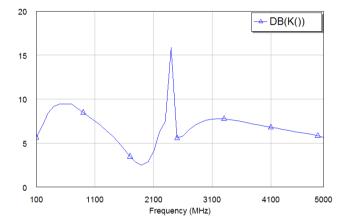

| Figure 91 - Stability factor K of the implemented TIA used for the experimental tests.                                                                                                                                                 |          |

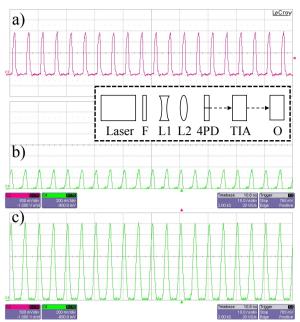

| that drives the VCSEL; panel b): the pulsed output voltage amplified by the TIA considering a single                                                                                                                                   | e        |

|                                                                                                                                                                                                                                        | 1        |

| illuminated PD; panel c): the same as panel b) for 4 illuminated PD of the 2x2 array. In the inset the optical act up used for the manufacture the logarity of VCSEL concerning 800 ng pulses at $\lambda = 50$ nm. F is a particular  |          |

| set-up used for the measurements: the laser is a VCSEL generating 800 ps pulses at $\lambda$ =850 nm; F is a neutral density filter to guitably attemute the laser neutral L1 and L2 are a negative and a positive feasel length lange |          |

| density filter to suitably attenuate the laser power, L1 and L2 are a negative and a positive focal length lens                                                                                                                        |          |

| forming a Galilean-type beam expander to magnify the laser beam spot for a uniform illumination of the 2x                                                                                                                              |          |

| PD array (4PD). The 4PD output pulse current is amplified by TIA and the voltage output pulse are analyse by the LeCray 8600A digital accillageone (0)                                                                                 |          |

| by the LeCroy 8600A digital oscilloscope (O).                                                                                                                                                                                          | 03<br>05 |

| Figure 93 - Experimental results performed at 500MHz in the same conditions of Figure 92.                                                                                                                                              | 92       |

### List of Tables

| Table 1 - Main characteristics of wireless biotelemetry systems in the literature.                       | 24 |  |  |  |

|----------------------------------------------------------------------------------------------------------|----|--|--|--|

| Table 2 – Power efficiency of transmitter (TX) and receiver (RX).                                        |    |  |  |  |

| Table 3 - Power Efficiency of the Transmitter (Tx) and Receiver (Rx) subsystems under different operatin | ıg |  |  |  |

| conditions.                                                                                              | 54 |  |  |  |

| Table 4 - CJ values for different BJT configuration.                                                     | 58 |  |  |  |

| Table 5 - Preliminary experimental results.                                                              | 62 |  |  |  |

| Table 6 -Developed tactile sensory feedback system: main specifications, performances and characteristic |    |  |  |  |

|                                                                                                          | 71 |  |  |  |

| Table 7 - Simulation results for different PD configurations and typologies.                             | 78 |  |  |  |

| Table 8 - a) Elements that composing the schematic of the current buffer in Figure 70 and b) Electronics |    |  |  |  |

| characteristics of the designed current buffer resulting from post layout simulations.                   | 79 |  |  |  |

| Table 9 - a) The sizes of the elements composing the schematic of the TIA shown in Figure 9; b)The       |    |  |  |  |

| electronics characteristics of the TIA resulting from post layout simulations                            | 80 |  |  |  |

| Table 10 State-of-the-art in implantable wireless biotelemetry                                           |    |  |  |  |

| 1 2                                                                                                      |    |  |  |  |

## Glossary

| Analog-to-Digital Converter                             | (ADC)       |

|---------------------------------------------------------|-------------|

| Photodiode                                              | (PD)        |

| Bit Error Ratio                                         | (BER)       |

| Light Emitting Diode                                    | (LED)       |

| Time Division Multiplexing                              | (TDM)       |

| Frequency Division Multiplexing                         | (FDM)       |

| Radio Frequency                                         | (RF)        |

| Electromyography                                        | (EMG)       |

| Electrocardiogram                                       | (ECG)       |

| Electroretinogram                                       | (ERG)       |

| Electrooculography                                      | (EOG)       |

| Medical Implant Communications Service                  | (MICS)      |

| Wireless Medical Telemetry Service                      | (WMTS)      |

| Industrial, Scientific and Medical                      | (ISM)       |

| Specific Absorption Rate                                | (SAR)       |

| On/Off Keying                                           | (OOK)       |

| Amplitude Shift Keying                                  | (ASK)       |

| Frequency Shift Keying                                  | (FSK)       |

| Phase Shift Keying                                      | (PSK)       |

| Bifase Phase Shift Keying                               | (BPSK)      |

| Quadrature Phase Shift Keying                           | (QPSK)      |

| Non-Return to Zero                                      | (NRZ)       |

| Near-Field Communication                                | (NFC)       |

| Radio Frequency Identification                          | (RFID)      |

| Vertical Cavity Surface Emitting Laser                  | (VCSEL)     |

| Ultra-WideBand                                          | (UWB)       |

| Pulse Position Modulation                               | (PPM)       |

| Low-Dropout Regulator                                   | (LDO)       |

| Synchronous On-Off Key                                  | (S-OOK)     |

| Data Acquisition System                                 | (DAS)       |

| DAS control unit                                        | (CU DAS)    |

| Transimpedance Amplifier                                | (TIA)       |

| Field-Programmable Gate Array                           | (FPGA)      |

| First In First Out                                      | (FIFO)      |

| Parallel In Parallel Out                                | (PIPO)      |

| master control unit                                     | (CU MASTER) |

| Phase-Locked Loop                                       | (PLL)       |

| Printed Circuit Board                                   | (PCB)       |

| Integrated Circuit                                      | (IC)        |

| Commercial Off-The-Shelf                                | (COTS)      |

| decoder control unit                                    | (CU DÉCOD)  |

| Flip-Flop                                               | (FF)        |

| D-type Flip-Flop                                        | (D-FF)      |

| Serial-to-Parallel Converter                            | (SPC)       |

| Pseudo-Random Number Generator                          | (PRNG)      |

| System-on-Chip                                          | (SoC)       |

| Impulse Based-Asynchronous-Address Event Representation | (IB-AS-AER) |

| Universal Asynchronous Receiver-Transmitter             | (UART)      |

| Full-Width-at-Half-Maximum                              | (FWHM)      |

| Lock-In Amplifier                                       | (LIA)       |

| True Random Number Generator                            | (TRNG)      |

| Look-Up-Table                                           | (LUT)       |

| Configurable Logic Blocks                               | (CLB)       |

| National Institute of Standards and Technology          | (NIST)      |

| Internet-of-Things                                      | (IoT)       |

| Industrial-Internet-of Things                           | (IIoT)      |

| True-Random Number Generator                            | (TRNG)      |

| Process-VoltageTemperature                              | (PVT)       |

|                                                         | · /         |

| Laser Transmission Spectroscopy                 | (LTS)       |

|-------------------------------------------------|-------------|

| Operational Amplifier                           | (OA)        |

| Phase                                           | (P)         |

| Quadrature                                      | (Q)         |

| Analog Front-End                                | (AFE)       |

| Second Generation Current Conveyor              | (CCII)      |

| Photovoltaic                                    | (PV)        |

| Duty-Cycle Corrector                            | (DCC)       |

| Double Data Rate Dynamic Random Access Memories | (DDR DRAMs) |

| Delay-Locked Loop                               | (DLL)       |

|                                                 |             |

#### ABSTRACT

In biomedical applications, optical communication links guarantee high data rates, low power consumptions and high electromagnetic compatibility. From these considerations, in this Thesis novel circuits and systems for optical data links in biotelemetry applications have been developed. More in detail, a complete biotelemetry system has been designed and implemented, both with discrete components and as full-custom integrated circuit. It includes digital architectures for the data coding/decoding, employing an UWB-based modulation technique, and analogue circuits to drive lasers and for the signal conditioning of photodiodes. The system has been firstly implemented and tested by using commercial devices so achieving data rates up to 300 Mbps with an energy efficiency of 37 pJ/bit and a maximum BER of  $10^{-10}$ . Subsequently, the developed solution has been suitably designed. at transistor level, for its microelectronic integration in AMS 0.35 µm standard CMOS technology and, after its fabrication, has been fully characterized with data rates up to 250 Mbps so obtaining an energy efficiency of 160 pJ/bit with a maximum BER of  $10^{-10}$ . Moreover, possible applications of the system are also reported, such as a neural recording system (work in collaboration with the Centre for Bio-Inspired Technology, Imperial College London, UK), a tactile sensory feedback system (work in collaboration with the COSMIC Lab, DITEN, University of Genova, Italy) and an event-driven serial communication on optical fiber for robotic applications (work in collaboration with iCub Facility, Istituto Italiano di Tecnologia - IIT, Genova, Italy). Furthermore, the acquired skills have been employed to design optoelectronic circuits and systems to be applied to optical transcutaneous oxygen sensing solutions that result to be particularly important for the fight against the COVID-19 pandemic. More in detail, different full-custom integrated photodiodes and analogue front-end circuits for their interfacing, as well as an optical wireless power transfer system, have been also developed (work in collaboration with the Worcester Polytechnic Institute, Worcester, USA). Finally, further related works, always concerning biomedical applications, are reported as appendices.

#### INTRODUCTION

The future electronic and optoelectronics systems for industrial, medical and life sciences applications will employ an increasing number of sensors to measure different physical and chemical parameters like pH values, humidity, temperature in exothermic and endothermic chemical processes, spatial parameters, object shapes and surface roughness. The data generated by the sensors must be acquired and elaborated to performing autonomous operations or parameters monitoring. For example, the improvements in biomedical engineering allow to extract and process information carried out by neural and biological signals and to control external electrics and electronics life-aid apparatus, like bodymachine and/or brain-computer-interfaces, with the aim to recover a satisfactory life quality of patients with physical and/or neurological diseases [1] [2]. In these regards, prosthetic limb, for example, must be equipped with arrays of tactile sensory systems interacting with the external environment to restore as much as possible the sense of touch of a human limb. Moreover, the stimulation of neuronal cells is useful against uncontrolled epilepsy [3]. Also, for the neuronal clinical applications a large number of sensors are necessary to record these signals that can come-from or go-to the brain cortical area by means of the design and implementation of implantable bidirectional biotelemetry links that connect specific internal parts of the patient body to be monitored or activated by external equipment.

The previous two applications are examples, similar to many others, that highlight the aim of the research in neuronal medical fields that, for many aspects, are not so dissimilar from those ones related to the developments of humanoid robots. All these applications have in common the acquisition of a large amount of data from different kinds of sensors, the elaboration of these data to permit autonomous decision-making activities with the subsequent elaboration of procedures for the activation of devices and/or the generation of stimuli. Typically, these analog signals must be transmitted from the sensors to a read-out circuitry that uses them as its input data.

The circuitry, in turn, provides the signal digital conversion by using an Analog-to-Digital Converter (ADC) and then, passes the digitized data to a processing unit. In general, the processing unit runs a statistical learning algorithm on the data to extract the meaningful information about the physical variations, for example in life-aid apparatus, of the touched object and, on this basis, drives a stimulator that provides to generate a series of electro-tactile stimuli understandable by the patient [4]. In this case, a large number of tactile sensors together with other types of sensors (depending on the specific application and use)

must be employed with fast response electronic circuitries for obtaining human-like touch sensing capabilities. Similar considerations can be done for the transcutaneous implanted systems that acquires neural signals and transfers them from inside to outside (and vice versa) of the patient body suffering physical and/or neurological diseases. The neural signals are analog electrical pulses detected by micro- and nano-sensor arrays directly inserted into the patient brain [5]. An implanted electronic circuitry is used to acquire the signals from these sensors and to digitally decode them in a form to be transmitted to external controlling and/or actuation devices. In this case, whatever be the transmission methodology, the implemented transcutaneous telemetries must operate at high data rates with exceptional energy-efficiency in terms of very low overall power consumption. This is an important system issue for ensuring the health of the patient since the power spent to activate the telemetry operations for the data acquisition and transmission is dissipated as heat in the tissue and can cause severe damage if the dermal thermal limits are exceeded. For this, the consequent specific requirement in transcutaneous implanted systems is to obtain their operation in the low-voltage and low-current regime [6] [7].

From the above discussed applications, it would be clear that the type of sensors to be employed is directly related to the specific applications but the general requirements are the design and fabrication of electronic analog/digital circuitries for the acquisition, elaboration and transmission of a very large number of data with fast response times (i.e., very large frequency bandwidth) to compel the requirements of an immediate response to stimuli and the activation of body-machines, prosthetics devices and/or brain-computerinterfaces.

In this Thesis are reported in detail the implementation of optoelectronic systems together with the electronic analogue and digital circuitries designed for the coding and decoding processes of the sensor-generated voltage signals for the applications above outlined: activation, control and transmission of stimuli for tactile sensory feedback in prosthetic devices; implantable biotelemetry system for neural signal recording and biological data monitoring. For these applications the transmission of the coded data towards the decoding circuitry is achieved by means of an optical link that is composed of a large bandwidth semiconductor laser and Si Photodiode (PD). As reported in the Literature, for the coded data transmission can be used different approaches like: (*i*) simple wire connections in percutaneous systems that are, however, uncomfortable and potentially cause of infections and diseases [8] and, (i), radiofrequency techniques employing antennas as the wide band transmitters and receivers [9]. The drawbacks of these approaches for the applications which are interested in, are the resulting poor electromagnetic compatibility and signal

integrity [10] and the increase of the electrical power as the operation frequency increases that can generate dermal injuries. Moreover, these data transmission techniques cannot be or are difficult to be integrated in small dimensions even if attempts have been recently reported in miniaturizing the radiofrequency devices [11].

On the other hand, the optical data transmission links based on optoelectronic components avoids all these drawbacks because they are ideally insensitive to electromagnetic disturbances (i.e., the optical carrier frequencies are many orders of magnitude higher than those ones of the electromagnetic radiation achievable with electronic circuitries), guarantee the best achievable signal integrity with minimum Bit Error Ratio (BER), can be fabricated using the standard Si CMOS integrated technology in micrometer square resulting area so allowing operations at very low-voltage and low-power. Moreover, as happens in the optical long/medium/short haul telecommunication networks, the achievable very large frequency bandwidth of the optoelectronic devices (i.e., laser and PD) and of the optical fibers used for the optical links allows using the same transmission channel to transmit the signals generated by different kinds of sensor arrays. This is an important advantage of the optical links respect to the other possible transmission technologies and greatly simplify the hardware of the prosthetic and biomedical devices. The latter is preferred to transmit data in prosthetic devices and in robots while the free space propagation is used in implantable system so avoiding the use of wired and radiofrequencies techniques [12].

The typical optical transmission link requires to accomplish the following implementation steps: (i) the ADC conversion of the sensor signals and the data pre-processing; (ii) the coding process for the generation of a sequence of digital data by using a suitable coding scheme for the transmission of also the Clock synchronization signal [13]; (iii) the generation of a sequence of current pulses replica of the digital ones; (iv) the generation of a sequence of laser pulses replica of the current ones; (v) the conversion of the sequence of laser pulses in a sequence voltage pulses generated by the PD; (vi) the transmission Clock recovery for the final decoding process and data post-processing. In the following paragraphs all these steps will be described in detail for tactile sensory feedback systems in prosthetics devices and for implantable biotelemetry systems. Due to the present Covid-19 global pandemic, another important application of optoelectronic systems is the measuring of respiration parameters such as the partial pressure of oxygen and carbon dioxide in the blood, the respiration rate, and the peripheral blood oxygen sensing technique have been reported [14]. Also in these cases, the systems require a light source (typically

semiconductor lasers or Light Emitting Diode (LED)'s emitting at some specific wavelength), PD and electronics circuitries necessary for the signal conditioning, such as transimpedance amplifier, driver and digital elaboration unit.

### 1. DATA LINK SYSTEMS - STATE OF THE ART

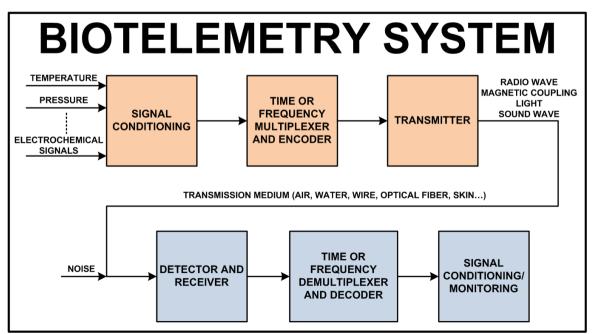

In this chapter, a generic data link architecture for biomedical applications, such as biotelemetry systems, is described. In particular, biotelemetry is a specific field of telemetry that permits transmission of biological information from a subject to a remote monitoring site as reported in Figure 1. The sensor signals are first converted to the electrical signals and after arranged for their transmission by employing Time Division Multiplexing (TDM) or Frequency Division Multiplexing (FDM) techniques. Then, the multiplexed signals are modulated according to the transmission line characteristics and transmitted toward the receiver system. Typically, the receiver is composed of a suitable detectors (i.e. for optical link a PD) and of amplifiers and filters able to regenerate the current or voltage signals coming from the detector. At this time, the information carried out by the signals are decoded and used as monitoring of biological parameters or as active feedback to drive control equipment. As shown in Figure 1, the biotelemetry systems can make use of Radio Frequency (RF) techniques or light free propagation for the wireless applications (e.g., for space satellite communication links) and coaxial cables or optical fibers for all those applications for which wireless transmission is not possible [15].

For example, if light is used to transmit information inside the body of a robot, in general, straight propagation is not available and the transmission can be easily obtained by employing an optical fiber. If now we restrict our attention on the implantable medical devices, they are electronic devices able to perform Electromyography (EMG), Electrocardiogram (ECG), Electroretinogram (ERG) and Electrooculography (EOG) of

Figure 1 - The block diagram of a generic biotelemetry system.

the patient by sending current signal probes to various parts of the patient body. In general, an implantable device consists of two subsystems: an internal subsystem located underneath the patient body skin and an external one acting as the controller of the all the operations to be performed. The external subsystem is also used for powering the implantable device and for sending the achieved data to external equipment, for example, for the physician monitoring.

Especially for implanted biotelemetry systems, several characteristics must be considered [16]:

- *Low Power Consumption*: Low power consumption is the main requirement for medical implantable devices where the large dissipation in power increases the possibility to damage the soft tissues of the human body. The changing of batteries or their recharging is, generally, inconvenient, difficult, costly and even risky for the patient; all implantable medical devices need to use as less as possible electrical power.

- *High Reliability:* A failure of the implantable medical device can produce pain, damage or even the death of the patient. Since device maintenance is also costly and risky for the patient, any effort must be done to guarantee the maximum possible reliability of the implanted devices.

- Low Voltage Signals: Most of the natural signals generated inside the human bodies (e.g., the neural signals) as well as the corresponding output signals of the electronic transducers are in the range from few tens of  $\mu V$  to 1 V. This means that special care must be done in sensing and amplifying the signals assuring, at the same time, to design and implement very low noise electronic conditioning circuitries.

- Low Frequencies: The frequency of biological signals varies from a fraction of Hz to several kHz, Moreover, most of the implantable devices are powered by low-frequency (<1 MHz) magnetically coupled coils that are often frequency modulated to include the data telemetry. Nowadays, the design of the implantable devices must comply the standard of the Medical Implant Communications Service (MICS) with a frequency band ranging from 401 MHz to 406 MHz [17].</li>

- *Small Size:* Implantable devices need to be as small as possible in size in order to be as small as possible invasive for the patient body. Taking into consideration the CMOS technology, this does not always mean that the silicon area should be as small as possible, because an increase the silicon area can be fruitful for including also external components and this can reduce the overall device complexity. In

addition, the use of some methods such as the auto-zeroing techniques, the FPGA paradigm and the artificial intelligence methodology can help to minimize the overall device size.

In recent years, numerous methods for the realization of low power and high data rate implantable RF biotelemetry transmitters have been presented in the Literature to perform wireless communications. The common implementation for these wireless transmitters is the use of the 433 MHz Wireless Medical Telemetry Service (WMTS) frequency band. A transmitter with the 433 MHz WMTS band presents advantages in the transmitter power consumption. in minimizing the free-space path losses and operation frequency. However, poor antenna efficiency due to reduced size of the implantable device is an unavoidable drawback. In order to reduce the size of the antenna in the transmitter, the use of the 2.4 GHz Industrial, Scientific and Medical (ISM) frequency band has been proposed but, for this frequency band, the power level of the transmitted signal is more attenuated by the human. The skin penetration depth  $\delta$  of an electromagnetic field is estimated by the following relation:

$$\delta = \frac{1}{\omega} \sqrt{\frac{\mu \varepsilon'}{2} \left( \sqrt{1 + \left(\frac{\sigma}{\mu \varepsilon'}\right)^2} \right)}$$

(1)

where  $\omega$  is the frequency of the signal,  $\varepsilon'$  the real part of the tissue permittivity,  $\mu$  the tissue permeability and  $\sigma$  the tissue conductivity. It is worth noting that, assuming for simplicity constant the material parameters, the skin penetration depth is inversely proportional to the frequency. Thus, RF devices using the 2.4 GHz ISM frequency band and those ones operating at higher frequencies are attenuated more than the devices working in the 433 MHz WMTS frequency band: this strongly limits the available penetration depth for the transmitters [18]. Another limit for a FR-based communication is the Specific Absorption Rate (SAR), defined as:

$$SAR = \frac{1}{V} \int \frac{\sigma(r)|E(r)|^2}{\rho(r)} dr$$

<sup>(2)</sup>

where  $\sigma$  is the sample electrical conductivity, *E* the RMS electric field,  $\rho$  the sample density and *V* the volume of the sample. The SAR is a measure of the rate at which the electromagnetic energy is absorbed per unit mass by a human body when exposed to electric fields with a frequency ranging between 100 kHz and 10 GHz. For example, in the European Union, for mobile phones and other similar hand-held devices, the SAR limit is 2 W/kg averaged over the 10 g of tissue absorbing most of the electromagnetic signal.

On the other hand, using light for the data transmission, the following advantages over the conventional RF telemetry are expected [19]:

- It is possible to achieve wide-band signal transmission relatively easily. This corresponds to the possibility of information transmission with a good frequency characteristic or a high-speed temporal response. In another view, it indicates the possibility of high-speed large-capacity transmission of information.

- It is possible to control much easier the electromagnetic interference respect to the RF telemetry. The light signal in optical telemetry does not produce interference effects with electromagnetic signals of other instruments. Moreover, also the shielding and securing safety can be done in a relatively easy way.

- The legal restrictions in using light for data communication are not as strict as for the RF-based systems.

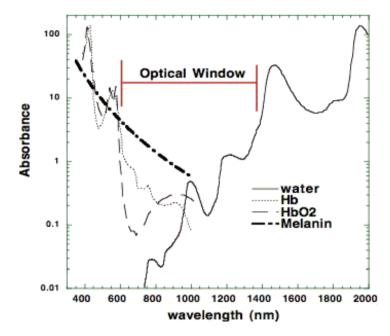

To design an optical biotelemetry system, it is necessary to choose the wavelength of the optical source featuring as the transmitter (i.e., the laser wavelength) on the basis of the absorption spectra of the major constituents of a human skin shown in Figure 2. Any wavelength of light, or ultraviolet-visible-infrared range, can be used for optical telemetry in principle. However, with ultraviolet light, the adverse effect on our health becomes a problem in a prolonged use. As for visible light, there may be a psychological effect on the subject. Further, in this wavelength, there are many sources of optical noise such as indoor lighting. With infrared light particularly of 700–1200 nm wavelength, such problems are few. Moreover, in this wavelength, the optical absorption of body tissue is relatively low, and we can expect high optical transmission through our body. For wavelengths less than 700 nm and greater than 1200 nm the absorption of the haemoglobin and water are predominant, respectively. Furthermore, for these wavelength values used in optical fiber communication, there are a large availability of semiconductor lasers and detectors.

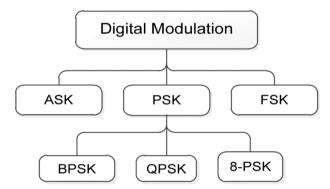

On the other hand, possible spatial misalignments between the optical source and the sensitive area of the photodetector represents the main disadvantage in optical wireless biotelemetry. Finally, for what concerns biotelemetry based on ultrasonic sources, these kinds of device can accomplish a good level of biocompatibility at the expenses of a low data rate and large transducer size. For these reasons, they are not suitable for implanted biotelemetry. Another important aspect in implanted biotelemetry systems is the choice of the modulation technique that impacts on the overall power consumption, bandwidth and system efficiency. Figure 3 shows the most common modulation techniques employed in biomedical devices [16].

Figure 2 - Absorption spectra of human skin constituents.

Figure 3 – Modulation techniques commonly used in biomedical devices.

Where Amplitude Shift Keying (ASK), Phase Shift Keying (PSK) and Frequency Shift Keying (FSK) are classic Amplitude, Phase and Frequency modulations, respectively. The transmission of multiple bit for each Symbol can be easily implemented in PSK modulations (i.e. Biphase Phase Shift Keying (BPSK), Quadrature Phase Shift Keying (QPSK) or 8-PSK).

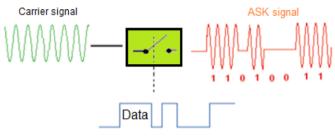

The ASK or On/Off Keying (OOK) is the simplest digital modulation used to implement wireless telemetry in bio-devices and biomedical implanted devices. In these types of modulation no carrier is used during the transmission and this help to minimize the power consumption of the modulator. The principle of ASK transmission is explained as shown in Figure 4 and Equation 3:

Figure 4 - Principle of ASK modulation.

where ASK is the modulated signal defined as the product of b(t) (the binary Data message) and c(t) (the carrier signal). The  $E_b$  is the bit energy and  $T_b$  the bit duration. Two are the methods used to operate the ASK demodulation: the coherent and non-coherent detection.

$$ASK(t) = b(t) \times c(t)$$

$$b(t) = \begin{cases} \sqrt{E_b} \text{ for } Data = 1 \\ 0 \text{ for } Data = 0 \end{cases}$$

$$c(t) = \sqrt{\frac{2E_b}{T_b}} \cos(\omega_c t)$$

(3)

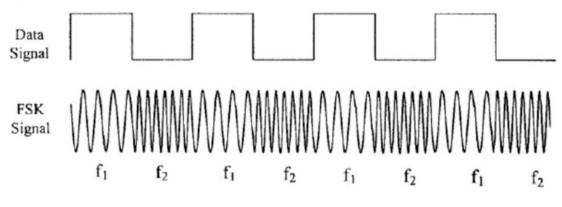

The coherent method employs the carrier phase information for the detection by means of a product detector and a phase-locked beat frequency oscillator. In the non-coherent methods, no carrier phase is used for the detection that is based on filtering the signal energy within allocated spectra and envelope detectors. From the characteristics of the two types of detection, the non-coherent method is that one more widely choose for its simplicity and low power consumption. In particular, the performance degradation of the non-coherent method is equal to about 1–3 dB if compared to that one of the coherent detection since it depends on the energy per bit to noise power spectral density ratio  $E_b/N_0$ . On the other hand, the operation principle of the FSK modulation technique is to send the binary data at two different frequencies. In the non-coherent FSK modulation, the two frequencies are associated to the transmission of the {1} and {0} as it is shown in Figure 5. The bit association can be simply represented by the following two relations:

$$S_{1}(t) = A \cos(2\pi f_{1} + \phi_{1}), \quad kT \le t \le (k+1)T \qquad bit = 1$$

$$S_{2}(t) = A \cos(2\pi f_{2} + \phi_{2}), \quad kT \le t \le (k+1)T \qquad bit = 0$$

(4)

where  $\phi_1$  and  $\phi_2$  are the initial phases at *t*=0 of the two sinusoidal waves that, in general, do not have the same value. *T* is the bit period of the binary data. This type of modulation can be generated by suitably switching the modulator output line between two oscillators.

Figure 5 - Principle of FSK modulation.

In the coherent type of FSK modulation, the two signals  $S_1(t)$  and  $S_2(t)$  must have the same initial phase  $\phi$  at t=0.

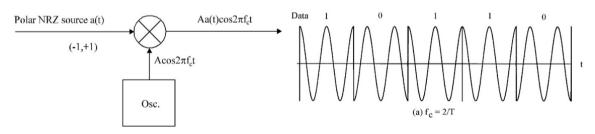

In the end, the simplest version of the PSK can be considered an ASK modulation where each Non-Return to Zero (NRZ) data bit of value 0 is mapped into a -1 and each NRZ 1 is mapped into a + 1. As shown in Figure 6, the resulting modulated signal can assume a value equal to the signals  $S_1(t)$  or  $S_2(t)$  with a phase variation of 180° coherent with the data that must be transmitted.

$$S_1(t) = A \cos(2\pi f_c), \quad kT \le t \le (k+1)T \qquad bit = 1$$

$$S_2(t) = -A \cos(2\pi f_c), \quad kT \le t \le (k+1)T \qquad bit = 0$$

(5)

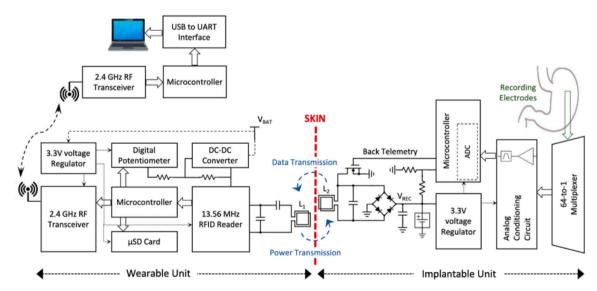

The data demodulation procedure for the PSK technique is more complicated than those ones for the ASK and FSK techniques, because it requires a carrier recovery system that must guarantee the best S/N versus BER values. Some examples of a complete data link system, representing the state-of-the-art for biotelemetry applications, are described in the following. In Ref. [20] it is proposed an implantable 64-channel closed-loop Near-Field Communication (NFC) system for real-time monitoring of gastric electrical activity. As shown in Figure 7, the system is composed by an implantable unit and an external unit.

Figure 6 - Principle of PSK modulation.

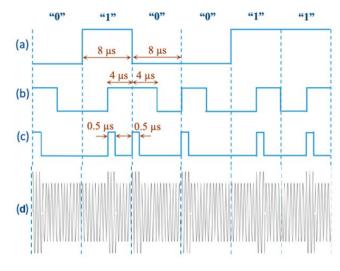

The internal unit is able to acquire, encode and transmit a bitstream through two coupled coils. The same coils are used also to provide power to the implantable unit. The external unit demodulates the incoming data using an envelope detector embedded in the Radio Frequency Identification (RFID) reader (TRF7970, Texas Instruments -TI-), decodes them by the microcontroller and perform a real-time monitoring through an ISM-band RF transceiver or stores the data locally on a microSD memory card. Moreover, the external unit manages the wireless power transfer towards the implantable unit. Starting from the bitstream to be transmitted, panel (a) in Figure 8, a Manchester encoding illustrated in panel (b) generates a transition '0'-'1' if a logic state equal to zero is transmitted or a transition '1'-'0' for the logic state one. The digital sequences of '0's and '1's are encoded by differential pulse position algorithm (see panel (c) of Figure 8) at the implantable unit, and the encoded data modulated over a 13.56 MHz carrier signal, can be seen by the envelope detector at the external unit (see panel (d) of Figure 8). In vitro studies demonstrated that the system can successfully records the signals akin to gastric bioelectrical activity from 64 independent channels with a sampling rate of 16 samples per second per channel through the inductive NFC at a data rate of 125 kb/s that simultaneously recharges the implantable unit local battery. In Ref. [21] is reported an optical telemetric link capable of providing a high data rate at a low power consumption for the transcutaneous transmission of neural signals. As well as the previous case, the telemetric link is designed for operation as the interface between an implanted cortical array and an external receiver, as reported in Figure 9.

Figure 7 – The detailed block diagram of a NFC communication system.

Figure 8 – Data coding algorithm of a pulsed Manchester encoding.

The basic principle of the communication system is very similar to a fiber optics communication link, but the transmission medium is fundamentally different. Human skin is a multi-layered material composed of epidermis, dermis and sub-dermis and, when a light beam passes through this layer stack, photons experience reflection, absorption and scattering. Thus, in order to collect the largest numbers of photons, the authors have used a Si photodiode with a large size of the sensitive area. The major drawback of this architecture is the reduced response time of the system because large sensitive area photodiodes have great junction capacitances limiting their operation bandwidth.

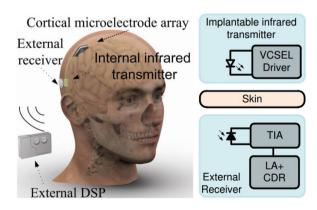

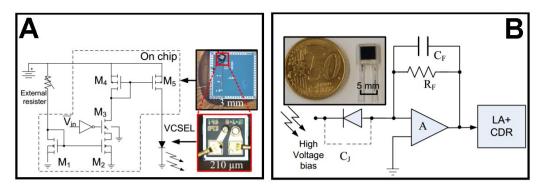

In Figure 10, the authors of Ref. 10 have realized an integrated low power current mirror circuitry for driving a Vertical Cavity Surface Emitting Laser (VCSEL) emitting at the wavelength of 850 nm (see panel A) and (see panel B) a transimpedance amplifier for the conditioning of s Si p-i-n photodiode.

Figure 9 - Block diagram of an optical transcutaneous link.

Figure 10 - Electronic interfaces of (A) the internal device and (B) the external device of an optical transcutaneous link.

The overall system is able to transmit data using a simple non-return-to-zero (NRZ) modulation though a 2.5 mm thick perfused tissue at a data rate of 100 Mbps with a BER  $<2\times10^{-7}$  (evaluated by using an FPGA board) and an overall electrical power consumption of 2.1 mW.

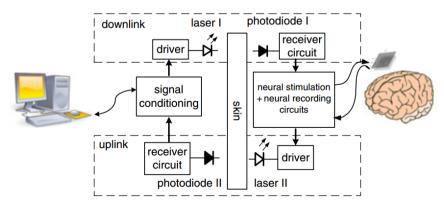

The same authors present in [22] a bidirectional optical transcutaneous telemetric link for brain machine interface. Using the bidirectional link reported in Figure 11, it is possible to observe neural activity and apply neural stimuli accordingly. However, it is important to avoid any form of optical cross-talk between the two communication channels that share the same transmission medium, as illustrated in Figure 12. The authors use a VCSEL emitting at 680 nm for the downlink transmit data from the external base unit to the implantable one. A second VCSEL emitting at 850 nm is utilised in the uplink for data transmission from the implantable unit to the external device. In order to avoid unintentional detection of the 680 nm downlink signal, an optical bandpass filter with a transmission efficiency of 95% is used to block this unwanted signal and allow most of the 850 nm signal to pass through the skin. In this way, in the optical downlink, the data are transmitted at the data rate of 1 Mbps through a 2 mm of porcine skin with a power consumption of 290  $\mu$ W in the implantable receiver.

Figure 11 - Block diagram of a bidirectional optical transcutaneous link.

Figure 12 - Scattering, absorption and reflection of an optical signal in human skin.

This corresponds to a transmission efficiency of 290 pJ/bit. In uplink, the data rate is of 100 Mbps with an electrical power consumption of 3.2 mW in the implanted transmitter. This corresponds to a transmission efficiency of 32 pJ/bit.

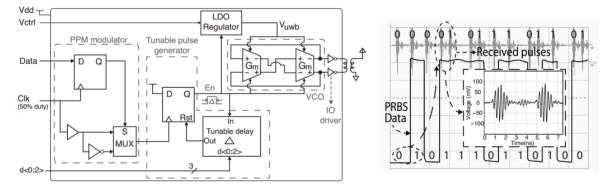

In Ref. [23] the authors propose a low-power, high data rate impulse Ultra-WideBand (UWB) RF transmitter. The system is shown in Figure 13. Starting from a clock signal and the data stream to be transmitted, the system generates a train of voltage pulses where the position of the pulses determines the transmitted bit implementing a Pulse Position Modulation (PPM). The generated pulses control a Low-Dropout Regulator (LDO) that supplies the oscillator. The transmitter occupies 0.055 mm<sup>2</sup> in 0.13µm CMOS technology and is capable of transmitting pulses at a frequency of 135MHz. The electrical power consumption is equal to 10pJ/bit. In Table 1, the comparison of achieved performances of the state-of-the-art of wireless biotelemetry solutions that can be found in Literature is presented. The results show that the optical data link is a good choice in biotelemetry applications, even if other solutions are commonly used.

Figure 13 – Block diagram of an IR-UWB transmitter architecture (on the left) and some related experimental results (on the right).

| Reference | Publication<br>Year | Bitrate<br>[Mbps] | Energy<br>Efficiency<br>[pJ/bit] | BER                | Implementation<br>Type       | Data Link<br>Type | Maximum<br>Operating<br>Distance<br>[mm] | Coding<br>Technique |

|-----------|---------------------|-------------------|----------------------------------|--------------------|------------------------------|-------------------|------------------------------------------|---------------------|

| [20]      | 2019                | 0.125             | 50400<br>(TX)                    | N.A.               | Discrete components          | Inductive         | 50                                       | LSK                 |

| [21]      | 2014                | 100               | 21                               | < 10 <sup>-7</sup> | Integrated TX<br>Discrete RX | Optical           | 2.5                                      | N.R.Z.              |

| [22]      | 2015                | 100               | 290                              | N.A.               | 0.35 μm<br>CMOS              | Optical           | 2                                        | N.R.Z.              |

| [23]      | 2013                | 135               | 10                               | N.A.               | 0.13µm<br>CMOS               | IR-UWB            | 120                                      | PPM                 |

| [24]      | 2015                | 67                | 30                               | < 10 <sup>-7</sup> | Integrated TX<br>Discrete RX | IR-UWB            | 500                                      | OOK                 |

Table 1 - Main characteristics of wireless biotelemetry systems in the literature.

### 2. OPTICAL DATA LINK - DESIGN AND IMPLEMENTATION

This chapter reports the implantable/transcutaneous biotelemetry architecture for brain machine interfaces designed and implemented by the candidate. The system uses a novel optical wireless communication system to achieve a highly energy-efficient link. The project was carried out in collaboration with the Centre for Bio-Inspired Technology of the Department of Electrical and Electronic Engineering - Imperial College London (UK).

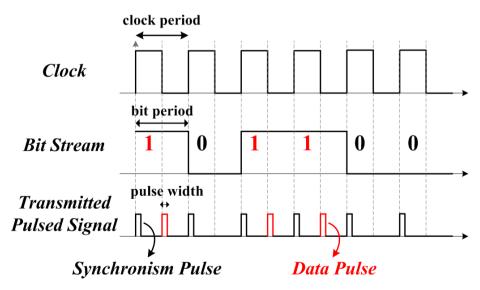

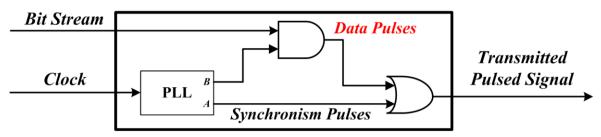

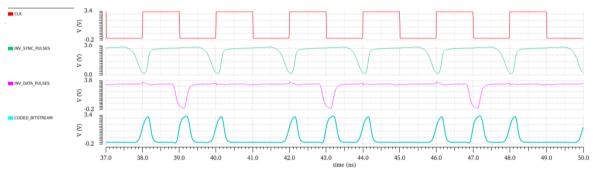

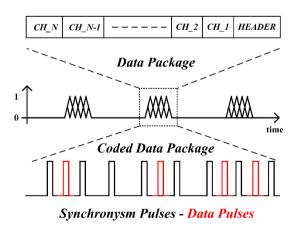

In particular, the time diagram shown in Figure 14 illustrates the used data coding process based on a Synchronous On-Off Key (S-OOK) modulation paradigm that is able to combine both the input bitstream and the clock signals. Starting from the top of the Figure 14, the first periodic waveform is the Clock signal. For each Clock period a bit {1} or {0} of the Bit Stream can be transmitted. The Clock signal is recognized by the decoding block because for each Clock period, a laser pulse is generated independently from which bit is transmitted.

Thus, this represents the Synchronism Pulse having the same period of the Clock signal and is used for the Clock recovery operation. Referring now to the Bit Stream waveform, for this timing architecture, if a bit {1} must be transmitted, a laser pulse is generated at a time corresponding to a half-period of the Clock signal. On the other hand, if a bit {0} must be transmitted, no laser pulse occurs at a time corresponding to a half-period of the Clock signal. Thus, the resulting Transmitted Pulsed Signal is formed by an aperiodic sequence of laser pulses where only those ones transmitting the Clock signal have a defined frequency. The described transmission paradigm is a modified version of the

Figure 14 - Timing diagram showing the data coding process using an S-OOK modulation.

classical OOK modulation scheme and has been designed for the systems that must operate in the low-voltage and low-power regime. Respect to the OOK modulation scheme, in fact, Figure 14 shows that the laser operates only for a time corresponding to the laser pulse duration that can be shorter or much shorter than the Clock period. For example, it is now possible to employ VCSEL devices able to generate laser pulses with a duration of few tens of picoseconds. As a consequence, the described mode operation minimizes the electrical power consumption of the overall optical transmission link.

The following Paragraphs describe the design, implementation and experimental results of the developed optical data link implemented using both discrete components and Integrated Circuit (IC) solutions.

#### 2.1. Design and implementation - discrete components solution

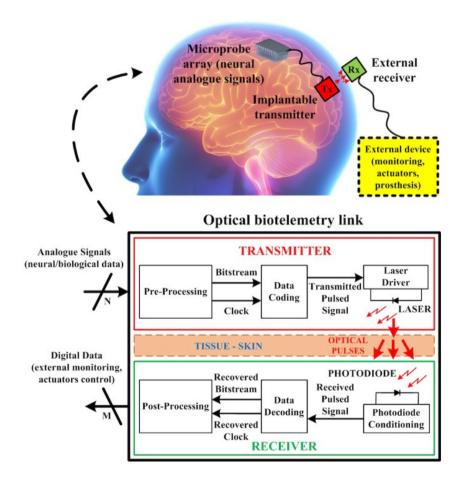

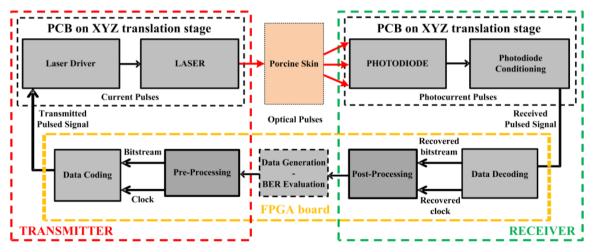

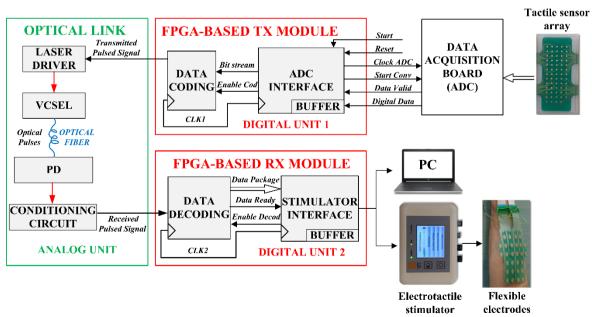

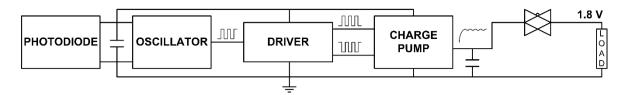

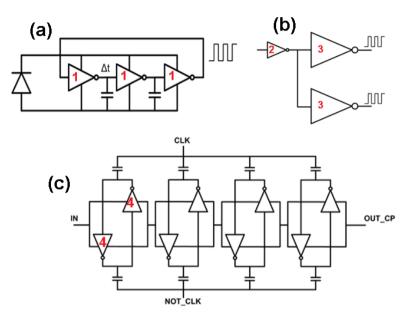

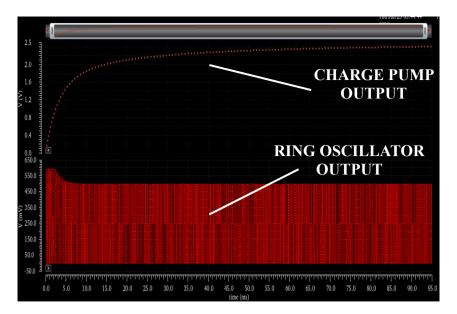

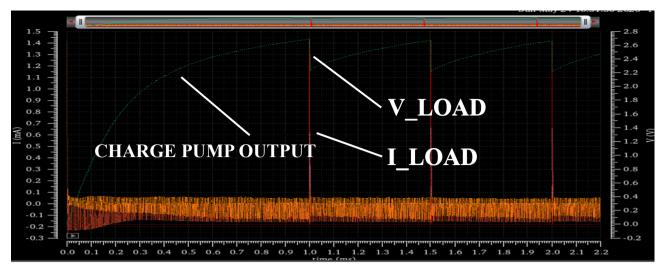

The overall scheme, reported in Figure 15, includes a microprobe array that acquires neural signals and convert them in digital signals (realized by the Imperial College London) and others analog/digital blocks which are described in the following Paragraphs of this Chapter. In particular, the Transmitter module is composed of three blocks and of a VCSEL. The first block (Pre-Processing) is a Data Acquisition System (DAS) that controls the acquisition and serialization of the data. The second block (Data Coding) performs the coding of the data that have been previously digitally converted and serialized. The output of this block is a sequence of voltage pulses suitably codified that must contain also a synchronization Clock signal needed to properly transmit and receive the information contained in the signal sequence generated by the sensors. The last block is the Laser Driver that receives in input the sequence of the coded pulses and transforms it in a sequence of current pulses, exactly a replica. This sequence of current pulses must have an amplitude greater than the threshold level to activate the VCSEL laser action (i.e., the amplitude of each current pulse of the sequence must exceed the value of the VCSEL threshold current). In this way, the VCSEL generates a sequence of laser pulses that is the counterpart of that one generated by the coding process. Thus, the digitally converted data containing the information on the changes of the physical/chemical parameters measured by the sensors are optically transmitted. Referring to Figure 15, also the Receiver module is composed of three blocks and of an optoelectronic device, the PD. The PD, usually a Si photodiode with frequency bandwidth equal or larger than that one of the VCSEL, generates current pulses that follow the same temporal shape of the transmitted laser pulses with amplitudes proportional to their intensities. By using an electrical scheme that employs a Transimpedance Amplifier (TIA), the output of the Photodiode Conditioning Block is a sequence of voltage pulses from which it is possible to obtain the information transmitted by the optical communication link through a suitable decoding operation performed by the Data Decoding Block. In the end, the data are elaborated by the Post Processing Block.

The system operates an UWB communication up to a data rate of 300 Mbps with a BER less than 10<sup>-10</sup>, and an energy efficiency of 37 pJ/bit, value estimated for a post integration system. The system can handle, for example, up to 16- bit 1024 channels of broadband neural data sampled at 18 kHz with only 11 mW of electrical power consumption.

The system was realized using discrete components (commercial components/custom PCB for analog blocks and a Xilinx KCU105 Field-Programmable Gate Array (FPGA) for digital blocks).

The following sub-Paragraphs describe the design of each sub-blocks presented in Figure 15, sorted according to the dataflow. Subsequently, the implementation of the system and the experimental results obtained are shown.

Figure 15 – Block scheme of the developed transcutaneous optical biotelemetry system.

# 2.1.1. FPGA implementation of a digital architecture for data pre-processing and UWB coding

The implementation of the data coding technique schematically discussed in the previous section, requires the design and the development of suitable digital architectures. The possible solutions must ensure reliable coding and decoding operations even at high data rate with an overall high-power efficiency. For these purposes, an FPGA-based architecture has been used for the preliminary implementation of the digital solutions and for the fast prototyping of the system using commercial discrete components. In particular, the following described architectures have been implemented on a Xilinx FPGA Kintex Ultrascale board even if the implemented digital solutions have been designed to be implemented also on other families of FPGA boards.

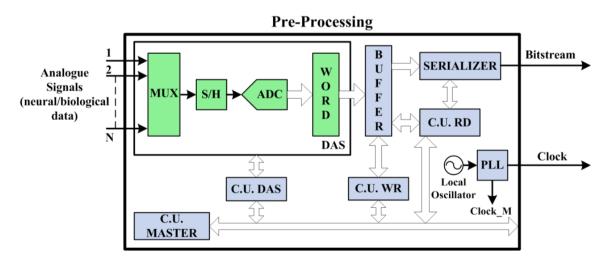

The function of the pre-processing circuit, reported in Figure 16, is to generate a single bitstream from multichannel sampled data by interleaving the different channels/samples using the TDM paradigm. This has been designed to process up to 1024 channels of data sampled at 18 kHz with a 16- bit resolution. The pre-processing circuit operates as follows: for each sample, the DAS control unit (CU DAS) sequences through all the data channels storing each 16-bit sample in the word register, First In First Out (FIFO) type Parallel In Parallel Out (PIPO) buffer). The word length is thus  $2 \times 8$ -bit. The initial portion of this register is pre-loaded with a pre-set starting sequence that forms the Header of the data packet. Each packet contains a single sample across all the 1024 channels (i.e., 2048 bytes) added to the starting sequence. In order to ensure that the output is a continuous bitstream (i.e., a continuous serialization of the composed data packages), the master control unit

Figure 16 - Pre-processing circuit, implemented on FPGA, showing the organisation of the different control units (CUs) for the data acquisition system.

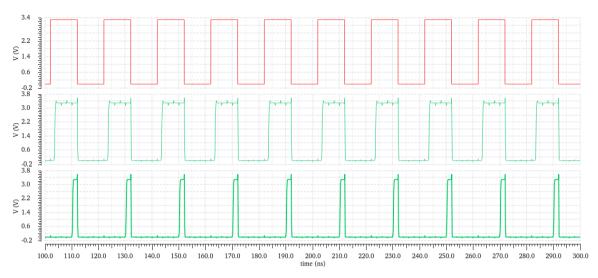

Figure 17 - Digital logic scheme of the Data Coding block.

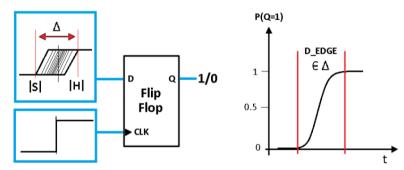

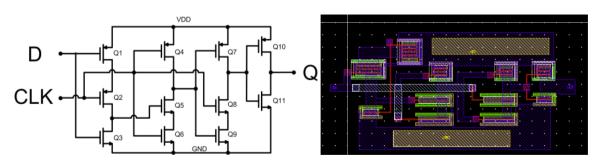

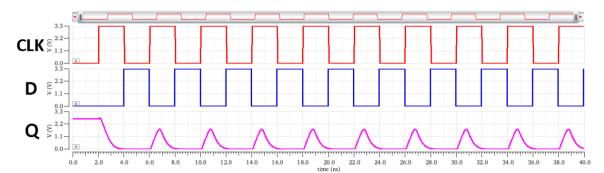

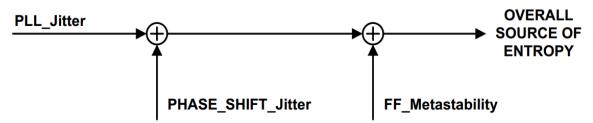

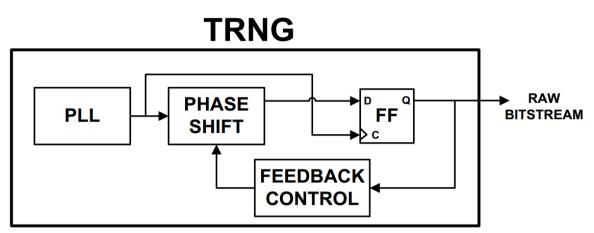

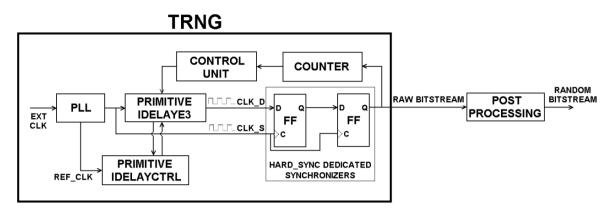

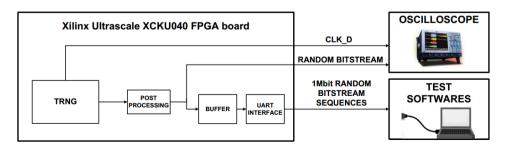

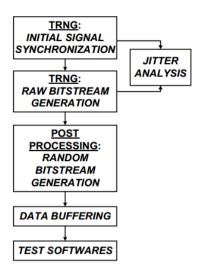

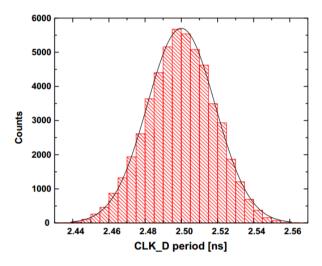

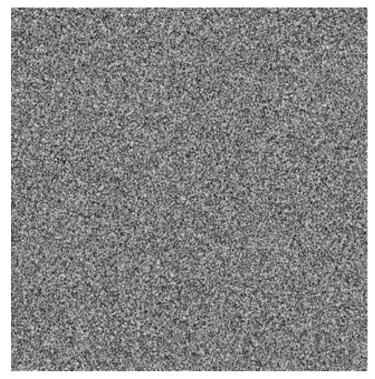

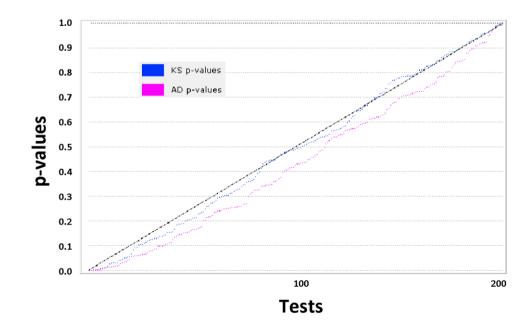

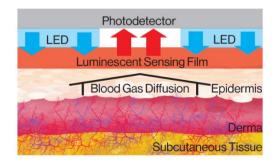

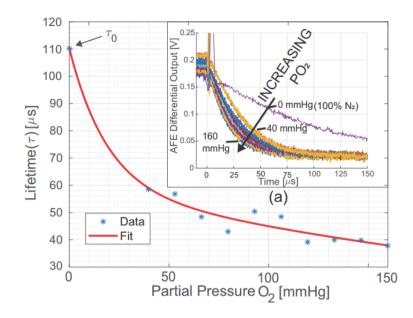

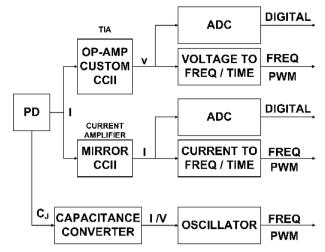

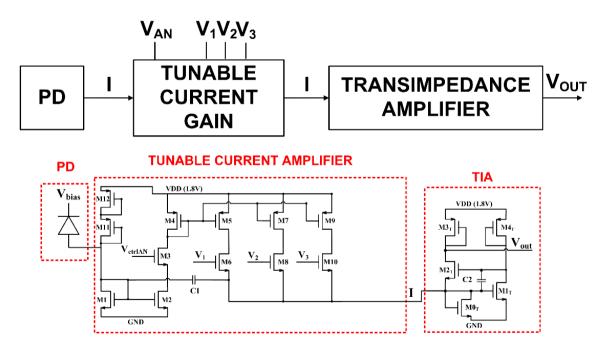

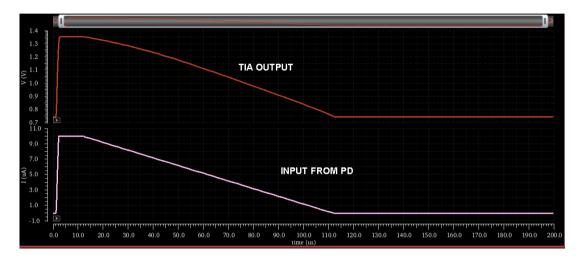

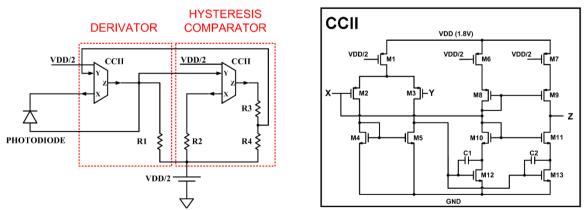

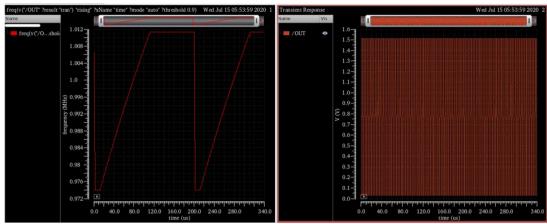

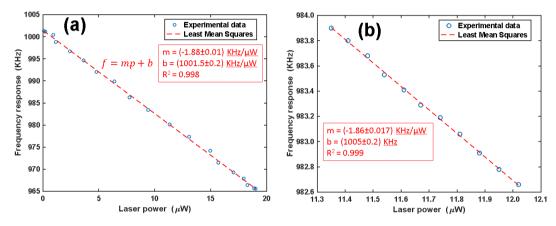

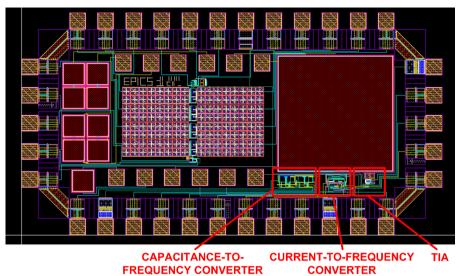

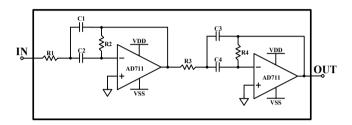

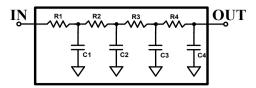

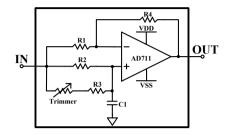

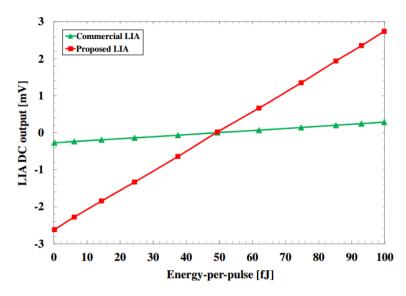

(CU MASTER) coordinates the timing of all the operations/functions (i.e., the data acquisition, data read and data write) of the overall pre-processing block. Additionally, a local oscillator provided on the FPGA board allows the implementation of a Phase-Locked Loop (PLL) block to provide an internal reference clock (i.e., Clock M @ 300 MHz) for the system synchronization.